# EUV 光罩檢測技術

# Extreme Ultraviolet Lithography Mask Inspection Technologies

李建霖、蔡佳勳、蔡坤諭 Chien-Lin Lee, Jia-Syun Cai, Kuen-Yu Tsai

此篇文章對於極紫外光 (EUV) 微影技術所須之具多層反射膜結構之光罩,其製造過程中需要之檢測技術之發展現況做一簡介,並提出一些展望。EUV 光罩之製程設計可採用許多和傳統光學光罩製程類似的步驟與設備,本文先由此出發做一簡介與比較,並指出幾個檢測 EUV 光罩特別之處。之後針對 EUV 光罩基底片 (mask blank) 製備過程之檢測技術做較深入之探討,並提出未來技術之發展方向。

This article introduces the current developments and prospects of inspection technologies which are necessary for the fabrication of EUV mask with a reflective multilayer structure. It can utilize many similar procedures and instruments used in the traditional optical mask processes into the design and manufacture of EUV mask one. In this article, it begins with a brief introduction and comparison, and also points out several particular aspects of EUV mask inspection. After that, it makes a further investigation about the inspection technologies throughout the fabrication of EUV mask blank. Finally, it indicates the direction of future development.

### 一、前言

摩爾定律 (Moore's law) 為美國英特爾 (Intel) 公司創始人之一暨名譽董事長戈登·摩爾博士根據產業觀察提出之經驗法則,其內容大致為積體電路上之電晶體數目約每兩年會增加一倍,換句話說即晶片之效能加倍或生產同樣效能晶片之成本減半,主要意義在於為半導體產業訂立經濟與技術發展重要趨勢指標(1)。半導體晶片之元件密度隨著摩爾定律逐年提升,其中製造端最關鍵的是微影製程解析度之演進。作為目前生產 7 奈米以下節點先進邏輯電路之量產微影技術,極紫外光微影 (extreme ultraviolet lithography, EUVL) 有別於傳統光學微影,多數材料對於 EUVL 所使用的 13.5 奈米波段光源吸收率都相當大,為提高效率,EUVL 需要在低真空環境下運作並且以反射式光學系統取代傳統穿透式系統,其中也包含光罩,因此目前 EUV 光罩結構為基於多層膜反射鏡之形式,並且需要奈米級的薄膜製備技術,其相關基本技術可於(2) 得到完整介紹。然而,現行 0.33 數值孔徑 (numerical aperture, NA) EUV 設備,根據 ASML(26,28) 相關文獻,其能達到之極限解析度大約在 13 nm。對於微影製程來說,解析度或是半間距 (half-pitch) 通常代指所能曝寫出的最小 1:1 線寬密集線圖案 (dense line/space pattern),因此其單次曝光大約 26 奈米間距之解析度極限仍難滿足國際設備和系統藍

圖 (international roadmap for devices and systems, IRDS) 3 奈米或 TSMC N3 節點<sup>(27)</sup> 所要求之最小 24/23 奈米問距。IRDS 預測至 3 奈米以下世代可能解決方案除前述 0.33 NA EUV 搭配多重曝光外,更高數值孔徑 (High-NA) 的 EUVL 技術亦是可行方案之一<sup>(3)</sup>,並且應可延用至目前預測之最小半間距 (IRDS 預測 2028 年以後電晶體將不再微縮而是改往三維堆疊發展以繼續提升效能)。而 High-NA EUV 微影關鍵之技術困難點包括光阻性能、符合產能需求之光源、低景深問題、光罩製作及檢測架構、成本等。微影設備商 ASML 近期已發表其第一代 0.55 NA EUV 設備<sup>(4)</sup>,產能可達 150 晶圓/小時,同時並持續研發更高功率之光源模組,以滿足 2025 年大量生產所需之大於 220 晶圓/小時產能。而雖然光罩上的圖案尺寸可放大四倍,但為滿足製像真確度所加入之光罩相位偏移及光學鄰近效應修正特徵圖案尺寸僅約晶圓上圖案的 1/2 大小,導致 High-NA EUV 光罩所能容忍的缺陷尺寸更加嚴峻,並且需要更精準的檢測技術以配合量產時程,凸顯光罩製作及檢測技術之重要性<sup>(5)</sup>。

從製程控制的角度來看,任何製程的開發與改善皆相當仰賴檢測技術來提供足夠的製程 資訊以利製程、設備與材料參數的適當調整。EUV 之光罩製程也不例外。由此觀點,廣義 之 EUV 光罩檢測技術包含其製程中所有會使用到的量測方法,包括基材平坦度、基材缺陷 度、多層膜缺陷度、多層膜反射度、吸收層反射度、光阻圖像品質、吸收層蝕刻後之圖像品 質與光罩整體成像品質等等。本文將先簡述 EUV 光罩製程及其檢測相對於傳統光學光罩之 重要區別,再進一步對檢測 EUV 特有之光罩基底片缺陷及所需之缺陷測試樣本製造方法做 探討。

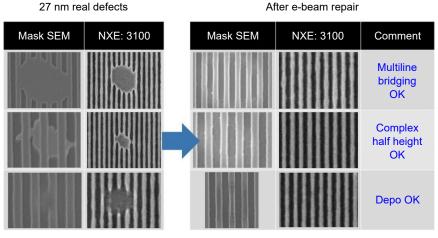

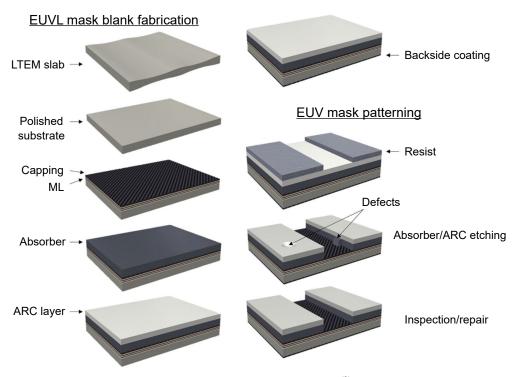

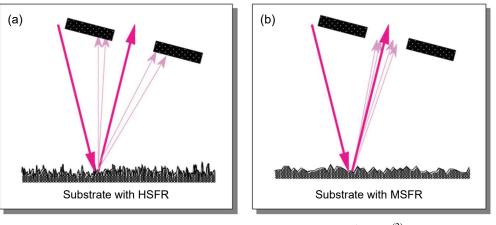

#### 二、EUV 光罩及其製程簡介

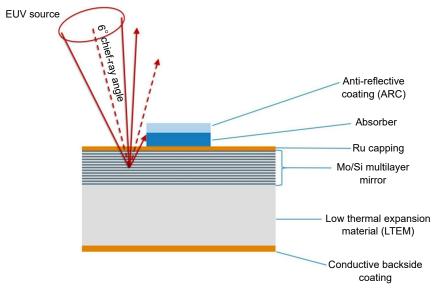

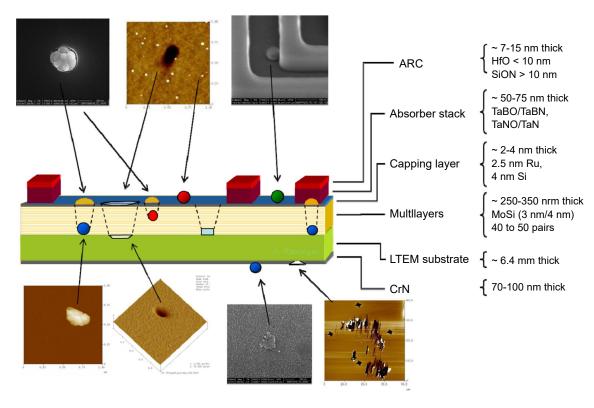

EUV 光罩由數層具有不同材料及光學功能的結構組成。目前常見之 EUV 光罩剖面如圖 1 所示<sup>(6)</sup>,光罩基板主要維持光罩之剛性及減少形變,因此需使用低熱膨脹係數材料並且其 表面須平滑無缺陷;而基板上的多層膜則是決定光罩效率的關鍵因素,為了提高反射率, 會採用光學常數不同的兩種材料交互堆疊,常見的多層膜是以 40 層鉬 (厚度 ~2.8 奈米)/砂 (厚度~4.1 奈米) 的雙層結構作為反射層,其理論反射率可達 75%,但因為鉬/矽介面會產 生中介層使反射率下降,透過介面工程引入可緩解中介層的影響,目前在13.5 奈米波段的 實際反射率大約為 70%;接著會在多層膜上鍍上保護層防止氧化造成的反射率損失,再度 上吸收層提高後續曝光圖案對比度,最後會再加上一層抗反射層以提高使用深紫外光 (deep ultraviolet, DUV) 檢測的效率;有些光罩會因後續製程設備需要而在背面鍍上導電層,以作 為靜電吸附 (electrostatic chucking) 使用,而後鍍完反射層的 EUV 光罩基底片再進行缺陷檢 測及修補後即可進行光罩吸收層圖案製作。光罩圖案製作基本上與傳統光罩製程類似,透過 光阻塗佈、電子束直寫曝光、顯影、蝕刻吸收層/抗反射層,再進行吸收層圖案缺陷檢測及 修補來完成。EUV 光罩吸收層可利用傳統光學光罩常用之光學檢測技術 (DUV 或電子束), 然而隨著製程節點進步,傳統檢測技術也須提升及檢測之缺陷信躁比,如引入解析度增進技 術來面對更小的缺陷尺寸 (如圖 2<sup>(7)</sup>),而吸收層圖缺陷修補主要使用電子束<sup>(8)</sup> 以減少對多層 膜的傷害 (如圖 3)。EUV光罩整體簡略製造流程如圖 4<sup>(2)</sup> 所示。大體來說,EUV 微影可視為 傳統光學微影的一種延伸,將其波長大幅縮小並把所有光學元件限制為反射式,其基本原理 並不難理解。EUV 光罩結構最大的不同是反射層的存在,其規格和製作的困難度卻與傳統 光學微影光罩有極大的不同。以應用於波長 13.5 奈米的反射式光罩來說,數奈米的表面粗 糙度即會造成足夠大的相位偏差破壞其原本的干涉效率,而表面的高頻/中頻空間粗糙度 (high/mid-spatial-frequency roughness, HSFR/MSFR, 如圖 5<sup>(2)</sup>) 也會使反射效率降低或是成為 邊緣粗糙度 (line-edge roughness, LER) 及放置誤差 (placement error) 的來源。相對於適用於波長 193 奈米的穿透式光罩,其困難度超過一個數量級。雖然因相關製程設備與材料的逐漸改善,大部分問題的根源及解決對策已被提出,但隨著製程節點不斷往前邁進,更多的結構需要 EUV 光罩,意味著檢測產能需求提升,而 High-NA EUV 光罩非對稱的微縮倍率也需要研發新的檢測技術。也因此,EUV 光罩的製作及檢測仍為 EUV 微影技術量產應用的困難關鍵點之一。<sup>(9)</sup>

圖 1. EUV 光罩剖面結構示意圖<sup>(6)</sup>。

| Technology Node (nm) | 28 | 22 | 16 | 11   | 8 |

|----------------------|----|----|----|------|---|

| Defect size (nm)     | 40 | 30 | 20 | < 10 | 7 |

| 193 nm inspection    |    |    |    |      |   |

| E-Beam inspection    |    |    |    |      |   |

圖 2. 使用 DUV 及電子束進行光罩檢測之可行性表 (綠色-可行; 黃色-需研發; 紅色-不可行) (7)。

圖 3. 使用電子束修復 EUV 吸收層圖案缺陷範例<sup>(8)</sup>。

圖 4. EUV 光罩製造流程示意圖<sup>(2)</sup>。

圖 5. 基板 (a) 高頻及 (b) 中頻空間粗糙度之影響示意<sup>(2)</sup>。

# 三、EUV 光罩缺陷

對於大部分的製程來說,缺陷是無法完全避免的,也是影響良率的重要因素。如何改善製程減少缺陷的產生,並對缺陷之檢測,清除,修補,與補償做一完整之技術發展與規劃,是製造無缺陷 EUV 光罩之關鍵。EUV 光罩之缺陷如圖 6,其分類方式大致如下:依可否被清洗程序清除者分類為軟缺陷 (soft defect) 及硬缺陷 (hard defect);依可否用修補製程清除者分類為可修補缺陷 (repairable defect 及不可修補缺陷 (non-repairable defect);而位於多層膜之缺陷對於成像品質之影響主要是亮度者為強度缺陷 (amplitude defect,成因多為接近表層之粒子或多層膜之瑕疵),主要影響建設性干涉者為相位缺陷 (phase defect,成因多為表面凹凸);如以光阻沖洗後對線寬等關鍵尺寸之影響者可分為可印出缺陷 (printable defect)及不可

印出缺陷 (nonprintable defect)。由於約 80% 多層膜反射層之缺陷來源為基板之缺陷<sup>(10)</sup>,因此控制基板缺陷成因及修復就顯得十分重要。在 EUV 光罩基底片的製備中,玻璃基板上之缺陷主要是因研磨製程產生,或是運輸過程中接受粒子汙染,此一現象亦會發生於多層膜反射層製程及吸收層製程中。基板及多層膜缺陷之大小在鍍上 EUV 多層反射膜後其效應會被縮小或放大,可透過沉積多層膜時加入額外製程來減緩其影響<sup>(11)</sup>,因多層反射膜之上幾層反射層反射大部分的光能量,相對而言下幾層反射層之非平坦缺陷對成像的影響小很多。由於 EUV 光罩組成複雜,其中任一缺陷皆有可能影響最終成像品質,因此 EUV 光罩基底片之缺陷檢測技術,必須包括玻璃基層之缺陷檢測 (substrate defect inspection),多層反射膜之缺陷檢測 (multilayer defect inspection),及吸收層之缺陷檢測 (absorber defect inspection)。

半導體產業常以能檢測之最小 PSL (polystyrene latex) 顆粒圓球直徑來定義一檢測機台的靈敏度。實測上可以在一基層上沉積不同大小的 PSL 顆粒加以檢測即可。對於 EUV 光罩基底片來說,由於無法以單一參數描述缺陷形狀,因此通常以等效球體積直徑 (spherical equivalent volume diameter, SEVD) 表示,常見之缺陷可以其形狀呈高斯分布的 SEVD 描述,需要透過缺陷高度與半高全寬 (full width half maximum,FWHM) 兩個參數來轉換。若可得知多層膜沉積製程對基板缺陷修復效應及光罩表面缺陷的可印出性,即可預測光罩基板的關鍵缺陷尺寸大小。

圖 6. 常見之 EUV 光罩缺陷示意圖(10)。

### 四、EUV 光罩基底片缺陷檢測技術

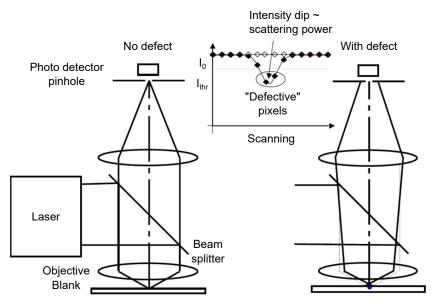

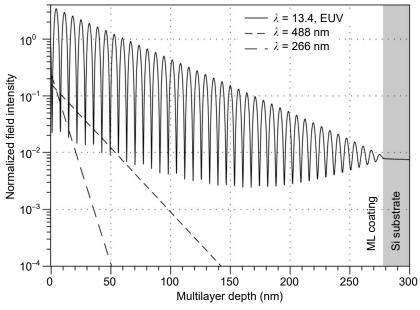

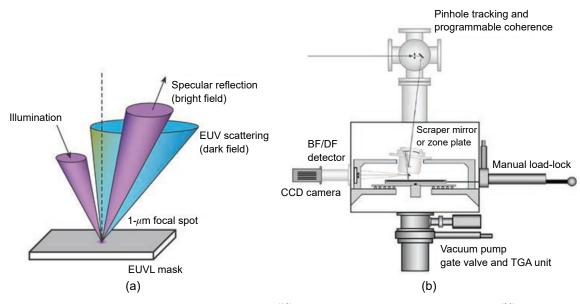

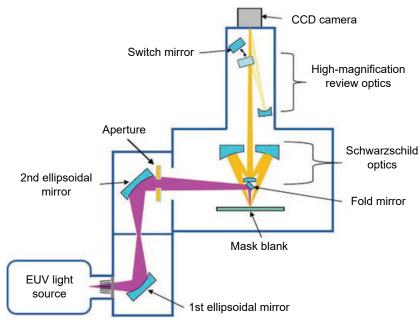

一般而言光學結構對入射光的反應會因其波長而改變。對於光罩而言,如果檢測光之波 長與光罩曝光之波長相同者稱為同波長檢測 (actinic inspection),否則稱為異波長檢測 (nonactinic inspection)。因為反射層與吸收層會影響成像品質,如果檢測訊號強度足夠,理論上 以同波長檢測較為合理,至於基材之檢測主要考慮檢測訊號強度即可。就 EUV 光罩缺陷檢 測技術的發展來看,目前光學異波長檢測主要沿用檢測傳統光罩之 DUV 檢測設備為主(12, 13), 如圖 7 所示之系統即是根據傳統光學微影光罩之檢測機台改進而成(14,15),以 488 奈米、266 奈米,或更短波長之雷射聚焦至基底片之表面,如果有表面缺陷吸收或散射此入射光,則在 共焦之感測器接受到的反射訊號將會減少,通常只要設定適當的偵測臨界值即可檢測出缺陷 的存在。理論上,這種方式可以檢測出無限小的缺陷。然而實際上因光機電系統有一定之雜 訊,以及表面粗糙度造成的散射,會造成檢測訊號中背景雜訊的存在,若與偵測臨界值太 接近的話,會導致許多的缺陷誤判 (false defect)。因此,檢測靈敏度提升的基本要點在於增 加缺陷訊號之對比並設法降低背景雜訊。這也是雖然異波長光無法穿透進多層膜深處 (如圖 8),但因為任何可印出之多層膜深處缺陷皆會在多層膜表面產生一定特徵,所以仍能使用 異波長光檢測 EUV 光罩基底片(17)。然而近年隨著製程節點邁向 3 奈米及以下世代異波長檢 測面臨其極限,若要確保所有可印出缺陷皆能被檢測出,同波長檢測即使用 EUV 波段光做 為檢測光源之技術便無可取代(18)。圖 9 為美國勞倫斯柏克萊國家實驗室 (Lawrence Berkelev National Laboratory, LBNL) 之同波長檢測系統示意圖,從同步輻射光源引進 EUV 光後以多 層膜反射鏡聚焦於基底片表面,其雙模式光路設計不僅可同時接收亮場式及暗場式偵測訊 號以增進缺陷檢出率 (capture rate),即掃描模式 (scanning mode);亦可插入一片由 EUV 波 帶片 (zone plate) 形成之物鏡成為 EUV 成像顯微鏡 (image mode) 做更精細的缺陷特徵檢測使 用。爾後隨著小型 EUV 光源開發成功也促進後續量產型同波長 EUV 檢測設備的發展。如 Lasertec 在 EIDEC 協助下發展之 EUV 光罩基底片同波長檢測設備 (actinic blank inspection, ABI),其原型機藉由增加數值孔徑,其檢測性能可支援至 16 奈米半間距製程節點(21),並進 一步拓展至包含吸收層圖案檢測之同波長檢測設備 (actinic patterned mask inspection, APMI) (22),其檢測能力可望應用至 High-NA EUV 所需的光罩檢測。而對於屬於玻璃材質的低熱膨 脹性基材來說, EUV 光的反射及穿透率太低, 因此其檢測仍需要使用異波長檢測。在此並 不會有使用更高的雷射強度損傷被測物的疑慮。

圖 7. 光學雷射掃瞄共焦顯微鏡做 EUV 光罩基底片之異波長檢測(14,15)。

#### EUV and UV field intensity in an Mo/Si multilayer coating

圖 8. 理論之不同波長光垂直入射多層膜之深度與強度關係圖(16)。

圖 9. (a) 亮場及暗場缺陷檢測示意圖<sup>(19)</sup> (b) 雙模式同波長檢測系統概念圖<sup>(20)</sup>。

EUV 多層反射膜與吸收層之反射度檢測主要是利用 EUV 反射儀 (reflectometer)。在早期 EUV 光源不易取得的時候,常將基底片送至具同步輻射光源 (synchrotron) 的研究中心之反射儀實驗站做量測<sup>(23)</sup>。目前隨著小型 EUV 光源的開發成功,已可將 EUV 反射儀縮小至一般製程機台大小而在光罩廠內部完成量測。

除了上述成像式缺陷檢測方法之外,亦能利用同調散射顯微鏡 (CSM) 來進行缺陷檢測,因其較為簡單的光學結構,可以通過增加測量角度的方式來提高空間解析度。這種無稜鏡系統可免於光學畸變,因此在理論上其解析度僅受限於繞射。其所運用的同調繞射成像

技術 (CDI) 可將繞射訊號重建為光罩圖像。由於 CSM 所收集到的訊號僅包含繞射訊號的強度,因而需要迭代式相位找回技術。然而迭代式相位找回含有大量的未知數,且提供了多餘訊息,所以迄今為止開發出的各種算法都對運算量有著極大的要求,導致 CSM 不能夠應付全光罩缺陷檢測。但是透過直接從繞射訊號抓取缺陷特徵的方法,可以使運算困難度大幅降低。模擬上,即使是 11 奈米線寬節點的空光罩缺陷檢測要求下設定之 4 奈米半高全寬,0.5 奈米高的缺陷都可以在 20 分鐘左右檢測出來。雖然該技術因為丟失相位訊息導致難以定位缺陷,但仍可利用快速掃描加上細節檢測的策略來進行技術性克服<sup>(24)</sup>。而在更微小精準的檢測性能標準測試樣本製作方面,電子束微影的解析度已稍嫌不足,引入解析度更高的氦離子束技術可望帶來有效改善<sup>(25)</sup>。

圖 10. Lasertec ABI 原型機光路示意圖<sup>(21)</sup>。

## 五、結論

本文對於 EUV 光罩之製程、缺陷與檢測技術之現況略加簡介與探討。為了減少成本與加速研發進度,EUV 光罩製程線應盡量採用既有之傳統光學光罩製程與設備。隨著半導體製程節點不斷為縮,基於 EUV 光源之檢測技術成可取得性對於成功量產 3 奈米及以下世代之半導體為重要關鍵因素之一,如今半導體開始往三維方向堆疊,除了微影製造技術本身的研發和突破,先進檢測技術與搭配的測試樣本亦是支撐半導體發展的幕後功臣。

#### 參考文獻

- 1. G. E. Moore, SPIE, 2437, 2 (1995).

- 2. Vivek Bakshi, EUV lithography, 2nd ed., Bellingham, Washington, USA: SPIE Press, (2018).

- $3.\ International\ Roadmap\ for\ Devices\ and\ Systems,\ https://irds.ieee.org/.$

- 4. J. G. Santaclara, et al., Optical and EUV Nanolithography XXXVII, 12953, SPIE, (2024).

- 5. Gerardo Bottiglieri, et al., "Anamorphic imaging at high-NA EUV: mask error factor and interaction between

demagnification and lithographic metrics", 32nd European Mask and Lithography Conference, 10032, SPIE, (2016).

- 6. Vu Luong, et al., Applied Sciences, 8 (4), 521 (2018).

- 7. Lior Shoval, et al, "Applicability of e-beam mask inspection to EUV mask production", *Extreme Ultraviolet (EUV) Lithography III*, **8322**, SPIE, (2012).

- 8. Markus Waiblinger, et al., "E-beam based mask repair as door opener for defect free EUV masks", *Photomask Technology* 2012, **8522**, SPIE, (2012).

- 9. Arosha Goonesekera, et al., Photomask Technology 2022, 12293, SPIE, (2022).

- 10. Abbas Rastegar, and Vibhu Jindal, 8352, SPIE, (2012).

- 11. Rajul Randive, et al., Emerging Lithographic Technologies XI, 6517, SPIE, (2007).

- 12. Nobutaka Kikuiri, et al., Photomask and Next-Generation Lithography Mask Technology XIII, 6283, SPIE, (2006).

- 13. Kwon Lim, et al., Photomask and Next-Generation Lithography Mask Technology XIII, 6283, 252 (2006).

- 14. A. R. Stivers, et. al., SPIE, 4889, 408 (2002).

- 15. J.-P. Urbach, J. Cavelaars, H. Kusunose, T. Liang, A. R. Stivers, Proceedings of the SPIE, 5256, 556 (2003).

- 16. Kenneth A. Goldberg, et al., Emerging Lithographic Technologies XI, 6517, SPIE, (2007).

- 17. Ted Liang, et al., *Photomask Technology 2015*, SPIE, **9635**, (2015).

- 18. Ted Liang, et al., Extreme Ultraviolet (EUV) Lithography XI, 11323, SPIE, (2020).

- 19. Anton Barty, et al., Emerging Lithographic Technologies IX, 5751, SPIE, (2005).

- 20. Yanwei Liu, et al, Emerging Lithographic Technologies IX, 5751, SPIE, (2005).

- 21. Takeshi Yamane, et al., Extreme Ultraviolet (EUV) Lithography VII, 9776, SPIE, (2016).

- 22. Arosha Goonesekera, et al., Photomask Technology 2022, 12293, SPIE, (2022).

- 23. E. M. Gullikson, S. Mrowka, B. B. Kaufmann, Emerging Lithographic Technologies V, 4343, 363 (2001).

- 24. Ding Qi, Kuen-Yu Tsai, and Jia-Han Li, "A new EUV mask blank defect inspection method with coherent diffraction imaging", (*Invited Talk*) 2014 International Workshop on EUV Lithography, Session 6: EUV Masks, Maui, Hawaii, USA, Jun. (2014).

- 25. Chien-Lin Lee, et al, J. Micro/Nanolithogr. MEMS MOEMS, 20 (2), 023001 (2021).

- 26. Klaus Hummler, et al. Optical and EUV Nanolithography XXXVII, 12953. SPIE, (2024).

- 27. Shien-Yang Wu, et al., "A 3nm CMOS FinFlex<sup>TM</sup> platform technology with enhanced power efficiency and performance for mobile SoC and high performance computing applications." *2022 International Electron Devices Meeting* (IEDM) 3-7 Dec, IEEE, (2022).

- 28. Jorg Zimmermann, et al., "Status and outlook of EUV optics at ZEISS." *International Conference on Extreme Ultraviolet Lithography 2023*, **12750**. SPIE, (2023).

#### 作者簡介

李建霖先生為國立臺灣大學電子工程學研究所博士,現為國立臺灣大學電機工程學系博士後研究 員。

Chien-Lin Lee received his Ph.D. in the Graduate Institute of Electronics Engineering from National Taiwan University. He is currently a Postdoctoral Fellow in the Department of Electrical Engineering at National Taiwan University.

蔡佳勳先生現為國立臺灣大學電子工程學研究所博士生。

Jia-Syun Cai is currently a Ph.D. student in the Graduate Institute of Electronics Engineering at National Taiwan University.

蔡坤諭先生為史丹福大學航太工程與電機工程博士,現為國立臺灣大學電機系副教授。

Kuen-Yu Tsai received his Ph.D. in Aeronautics & Astronautics Department and Electrical Engineering from Stanford University, USA. He is currently an Associate Professor in the Department of Electrical Engineering at National Taiwan University.