# P 型氧化鎵磊晶膜及功率二極體 應用之研究

# Study on the P-type Gallium Oxide Epitaxial Films and the Applications in Power Diodes

蔡欣穎、李承翰、洪瑞華 Xin-Ying Tsai, Cheng-Han Lee, Ray-Hua Horng

本研究針對 P型氧化鎵難以製備的問題,採用磷離子佈植技術成功實現 P型氧化鎵之研製,並應用於同質 PN 二極體製作。實驗結果顯示,經高溫退火活化後的磷摻雜氧化鎵具有正值霍爾電壓,證實其為 P型半導體,且電阻率可降至 1.01 Ω·cm,較未摻雜者下降約 9 個數量級。利用磷摻雜之 P型氧化鎵與矽摻雜 N型氧化鎵製作同質 PN氧化鎵二極體,為避免 P-side up 結構中因為高溫活化磷之製程產生矽擴散,進而造成的高漏電問題,本研究改採 N-side up 結構並使用 Re-growth 技術,有效抑制矽擴散,顯著改善整流特性,並將崩潰電壓提升至 979 V。此外,本研究亦製作氧化鎳/氧化鎵異質 PN 二極體,與同質二極體進行比較,發現同質二極體在可靠度與穩定性上表現更佳。本研究成果不僅證實 P型磷摻雜氧化鎵的可行性,也為未來高效能氧化鎵功率元件開發奠定基礎。

This study addressed the difficulty in fabricating p-type gallium oxide  $(Ga_2O_3)$ . Using phosphorus ion implantation, this research successfully developed P-type  $Ga_2O_3$  and applied it to the fabrication of homogeneous PN diodes. Experimental results showed that after high-temperature annealing and activation, the P-doped  $Ga_2O_3$  exhibited a positive Hall voltage, confirming its P-type semiconductor properties. The resistivity was reduced to  $1.01~\Omega\cdot cm$ , approximately nine orders of magnitude lower than that of the undoped  $Ga_2O_3$ . A homogeneous PN  $Ga_2O_3$  diode was fabricated using P-doped P-type  $Ga_2O_3$  and silicon-doped N-type  $Ga_2O_3$ . To avoid the high leakage caused by silicon diffusion during the high-temperature phosphorus activation process in the P-side-up structure, this study employed an N-side-up structure and regrowth technology to effectively suppress silicon diffusion, significantly improving rectification characteristics and increasing the breakdown voltage to 979 V. Furthermore, this study fabricated a nickel oxide/gallium oxide heterojunction PN diode. Comparisons with the homogeneous diode revealed that the homogeneous diode exhibited superior reliability and stability. This research result not only confirms the feasibility of P-type phosphorus-doped gallium oxide, but also lays the foundation for the future development of high-efficiency gallium oxide power devices.

# 一、簡介

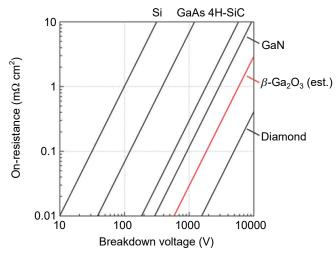

$Ga_2O_3$  被稱為超寬能隙 (ultra-wide bandgap, UWB) 材料, $\beta$ - $Ga_2O_3$  的能隙高達 4.6-5 eV  $^{(2-4)}$ ,因此臨界崩潰電場 (critical electric field, Ec) 可達 8 MV/cm  $^{(5,6)}$ ,此外, $\beta$ - $Ga_2O_3$  元件可以使用較短的漂移區 (drift region),進而  $\beta$ - $Ga_2O_3$  元件具有較低的開態電阻 (on-resistance) 與能源損耗。從理論上與其他半導體材料比較,在相同設計電壓下, $\beta$ - $Ga_2O_3$  元件具有較低的開態電阻;在相同開態電阻, $\beta$ - $Ga_2O_3$  元件具有較高的崩潰電壓 $^{(9)}$ ,如圖 1。不僅如此, $\beta$ - $Ga_2O_3$  的理論電子遷移率 (electron mobility,  $\mu$ n) 為 300 cm  $^2$ /V·s  $^{(7)}$ ,且具有高電子飽和速度 (saturation electron velocity,  $V_{sat} = 2 \times 10^7$  cm/s)  $^{(6)}$ ,以上此些特性說明  $\beta$ - $Ga_2O_3$  元件可以使用在大電流、大功率之元件,是下一世代功率半導體元件的熱門材料。在功率元件領域,常使用 Baliga figure of merit (BFOM =  $\epsilon\mu_n$   $E_C^3$ ) 評斷各種半導體材料, $\beta$ - $Ga_2O_3$  的 BFOM 指標之值為 Si 的 3444 倍  $^{(8)}$ ,是 GaN 與 SiC 之 4 倍與 10 倍  $^{(8)}$ ,如表 1,說明  $Ga_2O_3$  適合作為功率元件。

圖 1. 各種半導體材料的理論開態電阻與崩潰電壓之關係圖(9)。

|                                             | Si   | GaAs | 4H-SiC | GaN  | Diamond | $\beta$ -Ga <sub>2</sub> 0 <sub>3</sub> |

|---------------------------------------------|------|------|--------|------|---------|-----------------------------------------|

| $E_{G}(eV)$                                 | 1.1  | 1.4  | 3.3    | 3.4  | 5.5     | 4.9                                     |

| $\mu  (\text{cm}^2/\text{V}\cdot\text{s})$  | 1400 | 8000 | 1000   | 1200 | 2000    | 300                                     |

| E <sub>C</sub> (MV/cm)                      | 0.3  | 0.4  | 2.5    | 3.3  | 10      | 8                                       |

| $arepsilon_{	ext{REL}}$                     | 11.8 | 12.9 | 9.7    | 9    | 5.5     | 10                                      |

| $V_{SAT} (10^7 \text{ cm/s})$               | 1.0  | 1.2  | 2.0    | 2.5  | 1.0     | 1.1                                     |

| λ (W/m·K)                                   | 150  | 50   | 370    | 130  | 2000    | 10, 30                                  |

| BFOM ( $\mu \varepsilon E_C^3$ )            | 1    | 15   | 340    | 870  | 24661   | 3444                                    |

| JFOM $(V_{SAT}E_C)$                         | 1    | 2    | 17     | 28   | 33      | 29                                      |

| HMFOM $(E_{CV}\mu)$                         | 1    | 3    | 7      | 10   | 40      | 12                                      |

| HCAFOM $(E_{\nu}\mu E_{C}^{2})$             | 1    | 5    | 48     | 85   | 619     | 279                                     |

| HTFOM $(\lambda \varepsilon^{-1} E_c^{-1})$ | 1    | 0.23 | 0.36   | 0.10 | 0.86    | 0.01                                    |

表 1. 各種半導體的材料性質比較圖(8)。

雖然  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 可在大功率下操作,但相較於 GaN、GaAs、InP 等 III-V 化合物半導體,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 的電子遷移率較低,導致  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 元件的切換速度較慢,因此  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 元件常用於 1 GHz 以下的領域。

根據表 1 詳細的半導體材料性質比較表, $\beta$ - $Ga_2O_3$  材料最大的劣勢是其熱導率 (thermal conductivity),最高僅有 30 W/m·K,約為 Si 的五分之一<sup>(8)</sup>。功率元件在大電流操作時會產生大量的熱,若基板無法有效散熱,將導致元件快速升溫,儘管如此, 此一部分可以透過基板減薄、基板置換、異質磊晶於高導熱率基板等方式解決。

目前已有許多  $Ga_2O_3$  磊晶技術相關的研究,有多種方式可以成長  $Ga_2O_3$  薄膜,包括分子束磊晶 (molecular beam epitaxy, MBE)<sup>(17)</sup>、脈衝雷射沉積 (pulsed laser deposition, PLD)<sup>(18)</sup>、氫化物氣相磊晶法 (hydride vapor phase epitaxy, HVPE)<sup>(19)</sup>、霧化化學氣相沉積 (mist chemical vapor deposition, Mist-CVD)<sup>(20)</sup>、有機金屬化學氣相沉積法 (metal-organic chemical vapor deposition, MOCVD)<sup>(19)</sup>,然而在氧化鎵之研究中最大之挑戰為 P 型材料理論上無法製作而得,全球對於 P 型  $Ga_2O_3$  的研究也相對較少。P 型  $Ga_2O_3$  不易製備理論上有以下幾個原因;高活化能,使得電洞不易產生,且原生缺陷之氧空缺 (Oxygen vacancy) 導致電洞被補償掉,使得可移動的電洞減少,並且  $Ga_2O_3$  的價帶頂端非常平坦,因此有效電洞質量大,導致電洞遷移率低、電阻率高,種種因素使得高導電性 P 型  $Ga_2O_3$  理論上難以製備。缺少 P 型  $Ga_2O_3$  將導致功率元件結構設計受到限制,使得材料的優勢無法完全發揮。本研究為解決此一問題,特別採用磷離子植入技術,將磷植入 MOCVD 磊晶成長之  $Ga_2O_3$  薄膜,並以快速升溫退火製程用以活化磷離子,希望藉此得以製作而得 P 型  $Ga_2O_3$ ,研究並以製作 PN  $Ga_2O_3$  二極體,用以評估 P 型  $Ga_2O_3$ 之可行性。

# 二、研究方法

#### 2.1 離子佈植參數設計

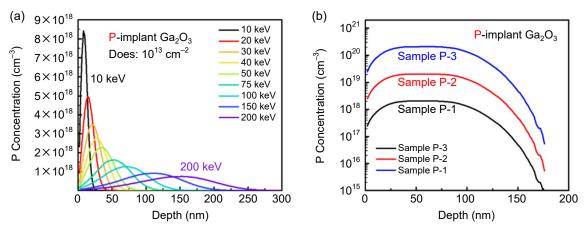

$Ga_2O_3$  為 III-VI 族化合物,當五族元素取代六族的氧,會產生電洞,形成 P 型  $Ga_2O_3$ ,本研究以離子佈植方式將 P 引入  $\beta$ - $Ga_2O_3$ 。首先利用 SRIM 模擬在各種植入能量下 P 離子佈植於  $Ga_2O_3$  的濃度分佈,結果如圖 2(a) 所示,濃度分佈呈現高斯分布 (Gaussian distribution),並隨著植入能量增加,植入深度隨之增加,而在相同能量下,植入元素的原子量越大,植入深度越淺。

圖 2. (a) P 離子佈植在不同佈植能量下的 SRIM 模擬結果圖 (b) P 多次離子佈植樣品之 SRIM 模擬結果圖。

藉由多次離子佈植的方式,達到約 100 nm 的均匀摻雜,每種元素皆設計三種總佈植劑量各差 10 倍的參數,詳細樣品與參數對照表請見表 2,其 SRIM 模擬請見圖 2(b)。

| Туре                                        | Sample name | Step | Energy (keV) | Dose (cm <sup>-2</sup> ) |

|---------------------------------------------|-------------|------|--------------|--------------------------|

| P-implant<br>Ga <sub>2</sub> O <sub>3</sub> | Sample P-1  | 1    | 100          | $1.6 \times 10^{13}$     |

|                                             |             | 2    | 50           | $1.0 \times 10^{12}$     |

|                                             |             | 3    | 40           | $2.5 \times 10^{12}$     |

|                                             | Sample P-2  | 1    | 100          | $1.6 \times 10^{14}$     |

|                                             |             | 2    | 50           | $1.0 \times 10^{13}$     |

|                                             |             | 3    | 40           | $2.5 \times 10^{13}$     |

|                                             | Sample P-3  | 1    | 100          | $1.6 \times 10^{15}$     |

|                                             |             | 2    | 50           | $1.0 \times 10^{14}$     |

|                                             |             | 3    | 40           | $2.5 \times 10^{14}$     |

表 2. P 多次離子佈植樣品之離子佈植參數表。

本研究依照以上之模擬,使用高溫 RTA 機台對 P 離子佈植樣品,並在氦氣的環境下以 1000 °C 1 分鐘進行退火活化。X 光繞射 (X-ray diffractometer, XRD)  $2\theta$  量測結果證實植入後樣品之 XRD 的半高寬都明顯增大、峰值位置 (peak position) 相較於 UID  $\beta$ -Ga $_2$ O $_3$  有略為降低,顯示晶格受創並且植入的離子位於間隙位置 (interstitial site),使得平面間距 (d-spacing) 增加;退火可有效修復缺陷。P 摻雜樣品退火後半高寬仍可以回復到未摻雜膜 (UID  $\beta$ -Ga $_2$ O $_3$ ) 的水準,而峰值位置相較 UID  $\beta$ -Ga $_2$ O $_3$  微幅右移則歸因於高溫下藍寶石基板 Al 擴散 $^{(10)}$ ,Al 的原子半徑小於 Ga,導致 d-spacing 稍微降低。

離子佈植樣品經過 1000 °C 1 分鐘退火活化之後,使用四點探針、高阻計進行電阻量測後,UID  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 之片電阻約  $6.65\times10^{13}$   $\Omega$ / $\Box$ ; P 摻雜  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 樣品,片電阻相比於 UID  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 大幅降低 7 個數量級至  $1.57\times10^6$   $\Omega$ / $\Box$ ,說明 P 非常適合作為  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 受體摻雜物。

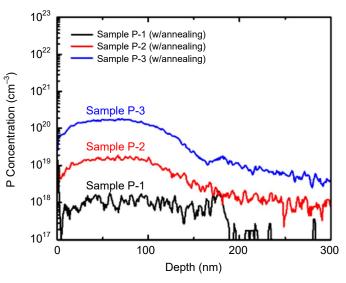

進一步利用 SIMS 進行縱深分析,量測結果顯示,低 (P-1)、中 (P-2)、高 (P-3) 三種摻雜劑量的 P 濃度依序為  $2\times10^{18}$ 、 $2\times10^{19}$ 、 $2\times10^{20}$  cm<sup>-3</sup>,如圖 3,與圖 2(b) SRIM 模擬結果相比較,在均匀摻雜區中的模擬與實際量測 P 濃度相近,但因通道效應 (channeling effect),導致 P 分布範圍擴展至藍寶石基板中。霍爾量測 (Hall measurement) 進一步驗證其 P 型特性:中、高劑量摻雜之樣品呈正霍爾電壓,電洞濃度分別為  $3.3\times10^{17}$  cm<sup>-3</sup> 與  $6.4\times10^{17}$  cm<sup>-3</sup>,對應活化率 1.65% 與 0.32%。 $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 的能隙約為 4.9 eV,紫外光電子能譜 (ultraviolet photoelectron spectroscopy, UPS) 能帶分析請參考 (Materials Today Advanced 20 (2023) 100436) (21) 圖 6(a)(b)(c),低劑量摻雜之樣品 EF-EV 為 3.82 eV,高於半帶隙一半,仍屬 n 型;而中、高劑量摻雜之樣品之 EF-EV 分別為 1.99、1.84 eV,小於二分之一能隙,為 P 型  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>,與霍爾量測結果吻合。

#### 2.2 P 離子佈植於氧化鎵之參數優化

針對先前 P 離子佈植  $\beta$ - $Ga_2O_3$ ,中、高劑量摻雜之樣品對應活化率僅有 1.65% 與 0.32% 的瓶頸,因此我們系統性地優化退火溫度、退火時間與 P 離子佈植劑量。

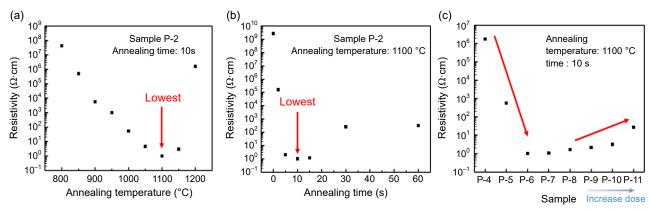

圖 3. 三個樣品 P 摻雜濃度 SIMS 圖。

- **1. 退火溫度的影響:**將中劑量摻雜之樣品 (P-2) 於 800 °C -1200 °C 10 s 快速熱退火後, XRD  $2\theta$  量測結果顯示,經過離子佈植後,( $\overline{2}01$ ) 的峰值位置從 18.899° 往左移動至 18.801°,而經過高溫退火後峰值位置逐漸往右回復,說明 d-spacing 會隨著退火溫度增加 而降低;然而超過 1150 °C,Al 擴散至  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 層,並且  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 裂解<sup>(11)</sup>,使得電阻值 快速上升,如圖 4(a) 所示。經過 UPS 分析, UID  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 的 EF-EV 為 3.51 eV,大於二分之一能隙,為 N 型;1000 °C、1100 °C 退火樣品的 EF-EV 分別為 1.93、1.15 eV,小於二分之一能隙,為 P 型。而 1200 °C 退火樣品的 EF-EV 為 2.85 eV,表示其 EF 非常接近 Intrinsic fermi level (Ei),所以其阻值非常高。1100 °C 退火樣品的 EF-EV 最低,表示其電 洞濃度最高,所以其電阻率最低,為最佳條件。

- 2. 退火時間的影響:將 P 離子佈植  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 樣品 (P-2) 在氦氣環境下以 1100 °C 進行不同時間的退火處理,退火時間分別為 2、5、10、15、30、60 秒。由 XRD 2 $\theta$  量測結果,退火時間增加可以改善其結晶性,降低半高寬,但超過 10 s 後 Al 擴散顯著, $(\overline{2}01)$  半高寬輕微回升且電阻率由最低 1  $\Omega$ ·cm 反彈至 300  $\Omega$ ·cm 等級,如圖 4(b) 所示。綜合以上,退火 10 s 為最適時間。

圖 4. Sample P-2 (a) 不同退火溫度 (b) 不同退火時間 與電阻率之關係圖 (c) 不同 P 離子佈植 劑量與電阻率之關係圖 (Sample P-4至P-11)。

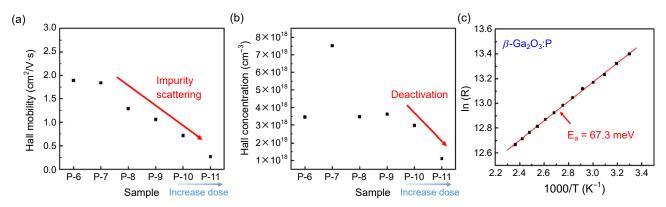

3. 磷離子佈植劑量之影響:Sample P-4 至 P-11 的劑量分別為 Sample P-1 的  $1 \cdot 5 \cdot 10 \cdot 20 \cdot 40 \cdot 80 \cdot 100 \cdot 200$  倍。根據前述結果使用最佳的退火參數,8 個樣品皆以 1100 °C 10 秒進行退火處理。離子佈植破壞造成峰值位置左移與半高寬增加;經退火後,結構大致恢復,但高劑量樣 (P-8 至 P-11) 仍殘留顯著缺陷。電性方面,隨著植入劑量增加,電洞濃度增加,使得電阻值下降,但劑量過高時電阻率又會上升,如圖 4(c) 所示。經霍爾量測發現,隨著植入劑量增加 (P-6 至 P-11),雜質散射 (impurity scattering) 影響程度增加,導致遷移率下降,而電洞的等效質量較大,使得 P 摻雜  $\beta$ -Ga $_2$ O $_3$  之遷移率皆僅有不到 2 cm $^2$ /V·s,如圖 5(a) 所示。另外,根據圖 5(b),過高的離子佈植劑量 (P-10、P-11),可能因為薄膜中 P 的含量增加,導致相鄰 P 原子的距離降低,因此在退火時容易兩個或多個 P 原子相互聚積,造成 P 無法有效取代 O 的位置,使得載子濃度降低 $^{(11,12)}$ 。根據 P 濃度與電洞濃度計算活化率,Sample P-6、P-7 活化率可達  $\approx 18$  %,對應電阻率 1  $\Omega$ ·cm。

最後,對 Sample P-6 進行變溫電阻量測,並繪製阿瑞尼斯圖 (Arrhenius plot),如圖 5(c) 所示,其活化能為 67.3~meV,如表 3~meV,如表 3~meV,相較於其中之各種摻雜物之活化能,雖然略高於 Si、Ge 施體摻雜物,但遠低於 N、Fe、Mg 等摻雜物,表示 P 非常適合作為  $\beta$ - $Ga_2O_3$  之受體摻雜物。

圖 5. 不同 P 離子佈植劑量與 (a) 遷移率、(b) 載子濃度之關係圖 (c) P 摻雜 β- $Ga_2O_3$  之阿瑞尼斯圖。

| 表 3. 4 | 各種 G | a <sub>2</sub> O <sub>3</sub> 掺杂 | 雜物的活 | 6化能 | 整理表 | 0 |

|--------|------|----------------------------------|------|-----|-----|---|

|        |      |                                  |      |     |     |   |

|                                                    | Activation energy (meV) | Туре           | Reference |

|----------------------------------------------------|-------------------------|----------------|-----------|

| Si-doped Ga <sub>2</sub> O <sub>3</sub>            | 15 - 31                 | N-type         | (12)      |

| Ge-doped Ga <sub>2</sub> O <sub>3</sub>            | 18 - 29                 | N-type         | (12)      |

| N-doped Ga <sub>2</sub> O <sub>3</sub>             | 355                     | P-type         | (13)      |

| Fe-doped Ga <sub>2</sub> O <sub>3</sub>            | 750 - 820               | semi-insulator | (14)      |

| Mg-doped Ga <sub>2</sub> O <sub>3</sub>            | 860                     | semi-insulator | (15)      |

| P-doped Ga <sub>2</sub> O <sub>3</sub> (this work) | 67.3                    | P-type         | -         |

# 2.3 不同結構氧化鎵 PN 同質二極體之分析與比較

利用 P 離子佈植 P 型  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 與 Si 摻雜 N 型  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 製作水平同質二極體,並分別製作「P-side up」與「N-side up」兩種同質 PN 二極體進行電性與材料分析。

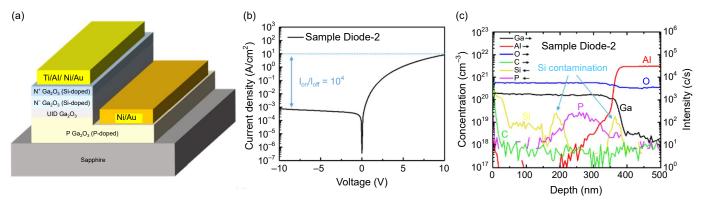

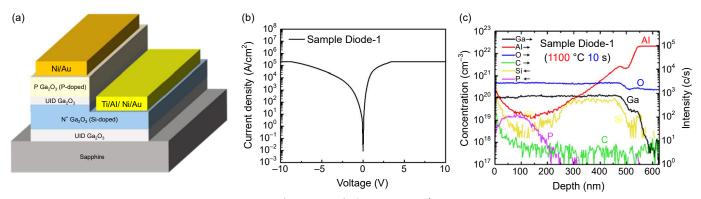

- 1. 製程差異:P-side up (Sample Diode-1) 先成長 N 型 Si 摻雜層,再將 P 植入上層的 UID  $Ga_2O_3$  並以 1100 °C 退火活化;N-side up (Sample Diode-2) 則先完成 P 型 β- $Ga_2O_3$  佈植與高溫活化,再使用 MOCVD 在樣品上 Re-growth N 型  $Ga_2O_3$ 。後者流程能避免 P 離子佈植後高溫活化造成 Si 擴散,結構如圖 6(a) 及圖 7(a)。

- 2. 電特性比較:Sample Diode-1 在  $\pm 2$  V 下僅得 24.7 的開關比,導通電壓 VF 僅 0.702 V,且逆偏 -8.6 V 即達量測極限;由 SIMS 縱深分析驗證表面處 Si 擴散濃度高達  $4.7\times10^{20}$  cm<sup>-3</sup>,遠高於 P 濃度,如圖 6(c),嚴重補償摻雜所產生的電洞,使元件性質接近蕭特基二極體。根據相關 Si 摻雜  $Ga_2O_3$  文獻,當退火溫度超過 950 °C,就會發生 Si 擴散的現象 (11),但根據 2.2 節之結果,以 1000 °C 以下無法有效活化 P 摻雜物,因此需要更改 PN 二極體的結構。Sample Diode-2 則相較 Sample Diode-1 有較佳之整流特性,其於  $\pm 10$ V 實現  $10^4$  的開關比  $(I_{on}/I_{off})$ 、4.394 V 導通電壓 (forward voltage, VF) 與 979 V 的崩潰電壓 (breakdown voltage, VBD);然而其理想因子  $\eta \approx 2.136$ ,顯示缺陷導致的漏電流與串聯電阻  $(0.533~\Omega\cdot cm^2)$  仍待優化。P-side up 與 N-side up Diode 比較表如表 4。

Sample  $I_{on}$  (A/cm<sup>2</sup>)  $I_{off} (A/cm^2)$  $I_{on}/I_{off}$ Sample Diode-1  $8.612 \times 10^4$  $3.480 \times 10^{3}$ 24.7 0.702 2.246 < 10 (@+2V)(@-2V) (P-side up)  $8.434 \times 10^{0}$  $8.107 \times 10^{-4}$ Sample Diode-2  $1.04 \times 10^{4}$ 4.394 2.136 979 (@-10V) (N-side up) (@+10V)

表 4. P-side up 與 N-side up Diode 電性比較表。

3. 材料分析:透過 SIMS 進行縱深分析,Sample Diode-1 經過 1100 °C 高溫退火活化摻雜物後,不僅 Al 擴散至  $\beta$ -Ga $_2$ O $_3$  磊晶層中,N 型  $\beta$ -Ga $_2$ O $_3$  區的 Si 也擴散至 P 型  $\beta$ -Ga $_2$ O $_3$  區,如圖  $\delta$ (c)。Sample Diode-2 透過 SIMS 仍發現 Re-growth 介面存在 Si 汙染,如圖  $\delta$ (c),推測係因製程汙染所致。由 XRD 搖擺曲線之結果,請參考 (Materials Today Advances 22 (2024) 100499)(22) Fig  $\delta$ (a),UID  $\delta$ -Ga $_2$ O $_3$ 、P 離子佈植後、退火活化後與 Re-growth 後其半高寬依序為  $\delta$ (a)。1.683°、2.407°、2.262°,顯示 P 離子佈植並未惡化晶格,反而可能填補點缺陷而略降半高寬。AFM 量測結果,請參考 (Materials Today Advances 22 (2024) 100499)(22) Fig  $\delta$ (a)。(d),UID  $\delta$ -Ga $_2$ O $_3$ 、P 離子佈植後、退火活化後與 Re-growth 後的表面粗糙度分別為  $\delta$ -Sa $_2$ O $_3$ ,這造成表面粗糙度和微提升,Re-growth 最表層為了降低接觸電阻而採用重摻雜之  $\delta$ -Ga $_2$ O $_3$ ,這造成表面粗糙度又進一步提升至  $\delta$ -Ga $_2$ O $_3$ ,可以為  $\delta$ -Ga $_2$ O $_3</sub> 的單斜結構。$

圖 6. Sample Diode-1 (a) 結構圖、(b) 半對數軸 I-V 特性圖、(c) SIMS 分析圖。

圖 7. Sample Diode-2 (a) 結構圖、(b) 半對數軸 I-V 特性圖、(c) SIMS 分析圖。

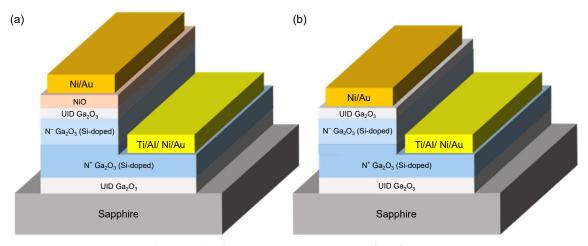

#### 2.4 不同退火溫度氧化鎳/氧化鎵 PN 異質二極體之分析

NiO 為 P 型半導體材料,使用濺鍍的方式沉積 NiO 於 N 型 Si 摻雜  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>,即可製作 PN 異質二極體,然而,濺鍍 NiO 的品質不佳,需要經過退火,以提升薄膜與介面品質,本節將討論不同退火溫度 NiO/Ga<sub>2</sub>O<sub>3</sub> PN 異質二極體的特性。

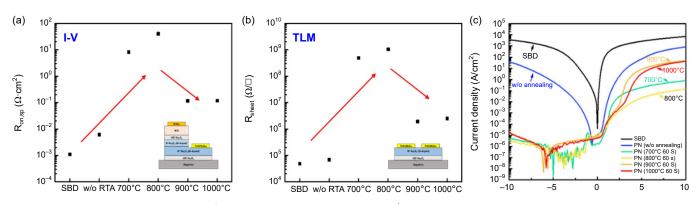

- 1. 基本電性分析:單純  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 蕭特基二極體 (Sample Diode-3,結構如圖 8(b)) 因缺乏 NiO 層而逆偏漏電極高,開關比僅 1.96;在界面引入 NiO 後 (Sample Diode-4,結構如圖 8(a)),接面能障提升使漏電流下降約兩個數量級,開關比攀升至 22.55。進一步分別在 700 °C、800 °C、900 °C、1000 °C 退火 (Sample Diode-5~8) 可進一步大幅抑制漏電流, 導致開關比分別飆升至  $1.39\times10^5$ 、 $4.03\times10^4$ 、 $2.69\times10^6$ 、 $2.42\times10^6$ ;開啟電壓隨溫度由 3.012 V 遞增至 4.129 V,顯示薄膜及介面品質隨退火優化而提升勢壘高度。高溫退火也大幅改變元件的開態特性,每個元件特徵導通電阻值 ( $R_{on, sp}$ ) 整理於圖 9(a),隨著退火溫度增加,電阻值先上升後下降,與 N 型  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 區的 TLM 之量測結果有相同趨勢,如圖 9(b),因此可以推測是 N 型  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 的阻值改變,造成元件的開態電流改變。

- 2. 崩潰電壓分析: 功率元件非常注重崩潰電壓,崩潰電壓越高的元件可以應用在更高電壓的領域。改變元件之電極間距,當元件的電極間距增加,雖然會增加串聯電阻,但是在大逆偏電壓下,其電場下降,能有效提升元件的崩潰電壓。退火 700 °C 與 800 °C 樣品因高阻值因而能承受更大之跨壓,於 10 μm 電極距離即取得 > 500 V 崩潰電壓,20 μm 距離

更分別達 1096 V 與 932 V ;反之, $900 ^{\circ}\text{C}$  與  $1000 ^{\circ}\text{C}$  樣品雖導通電阻較低,但因 N 型層電阻不足以承受大電壓,於  $20 \, \mu\text{m}$  電極距離崩潰電壓降至約  $250 \, \text{V}$  。

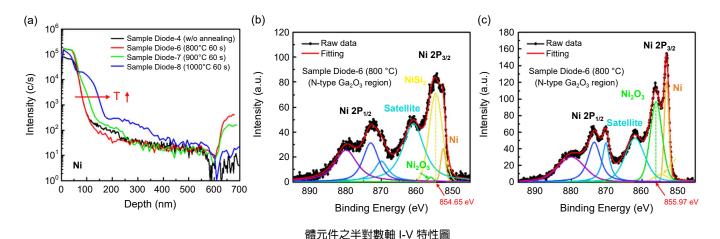

3. 材料分析:為進一步了解電阻值在退火溫度 900 °C 與 1000 °C 時下降的原因。首先使用無沉積 NiO 的  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 磊晶片進行一分鐘不同溫度的退火處理,發現 800 °C 至 1000 °C 的電阻值差異不大,代表阻值大幅變動是受到 NiO 的影響。進一步在 SIMS 分析中,發現 Ni 在退火時擴散至  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 層中,如圖 10(a),因此對 800 °C 與 1000 °C 樣品的 N 型  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 區進行 XPS 分析,如圖 10(b) (c)。XPS 分析顯示,800 °C 樣品中 Ni 主要以 NiSi<sub>2</sub> (85.5%) 存在,說明 Ni 與 Si 結合,造成 N 型  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 的電子濃度下降,並顯著提高電阻;1000 °C 樣品則以 Ni<sub>2</sub>O<sub>3</sub> (64.3%) 及金屬 Ni 為主,NiSi<sub>2</sub> 比例驟降至 6.5%,解釋其電阻回落與載流子濃度回升。

在本節中發現退火會導致 Ni 擴散,未來可以增加 UID  $Ga_2O_3$  層厚度或是調整退火時間,以避免 Ni 擴散至 N 型  $Ga_2O_3$  中,而影響其電子濃度。

圖 8. (a) NiO/Ga<sub>2</sub>O<sub>3</sub> 異質 PN 二極體 (Sample Diode-4~8) 結構示意圖、(b) Ga<sub>2</sub>O<sub>3</sub> SBD (Sample Diode-3) 結構示意圖。

圖 9. (a) 各元件的特徵導通電阻比較圖、(b) 各元件  $N^+$   $Ga_2O_3$  區之片電阻量測結果圖、(c) 不同二極體元件之半對數軸 I-V 特性圖。

圖 10. (a) 不同退火溫度 NiO/Ga<sub>2</sub>O<sub>3</sub> 樣品 SIMS 分析之 Ni 濃度分布圖經過 (b) 800 °C、(c) 1000 °C 退火樣品之 N型 Ga<sub>2</sub>O<sub>3</sub> 區 Ni 2p XPS 分析圖。

#### 2.5 氧化鎵同質與異質 PN 二極體之比較

本節比較 N-side up 同質 PN 二極體 (Sample Diode-2) 以及分別經過 700 °C、800 °C、900 °C、1000 °C 1 分鐘退火處理之 NiO/Ga $_2$ O $_3$  異質 PN 二極體 (Sample Diode-5 至 Diode-8),並且固定電極間距為  $10\,\mu{\rm m}$ 。

- 1. 基本電性比較:開態電流方面,未退火的同質二極體在 +10 V 時輸出電流 8.43 A,理想因子  $\eta=2.136$ ;異質二極體因 Ni 擴散抑制 n 型載子濃度,導致導通電阻大幅飆升,700 °C 退火樣品電流 1.23 A/ $\eta=4.58$ ,但 800 °C 退火樣品電流僅 0.216 A、 $\eta=11.76$ ,雖然開態電流較低,但可藉由採用指插電極之設計,降低開態電阻。逆偏漏電流方面,異質二極體 Sample Diode-5 至 Diode-8 的逆偏漏電流都很低  $(10^{-5}\sim10^{-6}\text{ A})$ ,同質 PN 二極體因 Re-growth 介面有較高的 Si 濃度,導致其漏電流偏大 (10-4A)。崩潰電壓方面,異質二極體 900 °C/1000 °C 退火樣品雖然開關比較高,但其崩潰電壓分別僅有 184、185 V,700 °C/800 °C 退火樣品可達 500 V 以上;同質 PN 二極體因  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 能隙略高於 NiO,具有高達 979 V 的崩潰電壓。

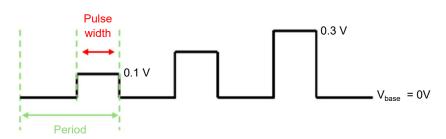

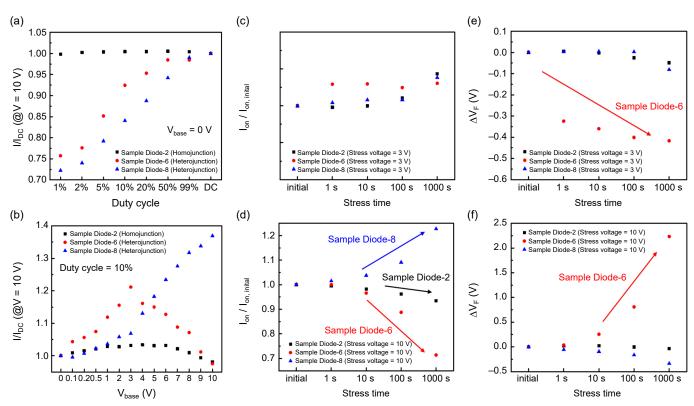

- 2. 暫態特性分析與比較:脈衝量測之波形示意圖如圖 11。首先對異質二極體 800°C/1000°C 退火樣品 (Diode-6/Diode-8) 及同質二極體 (Diode-2) 進行不同 Duty cycle 的脈衝量測, Vbase 為 0 V,三種元件量測結果如圖 12(a) 所示。因 Vbase 為 0 V,在 0 V 時無電流流經元件,不會提升元件的溫度,所以 Duty cycle 越大,0 V 佔比越小,越容易有熱累積,導致元件升溫,進而造成開態電流增加,由 Diode-6 及 Diode-8 量測結果可觀察出此趨勢;然而對於 Diode-2,在不同 Duty cycle 下的開態電流幾乎無變化,推測是因為同質接面,熱穩定性較佳。另外,在 10% Duty cycle下,對三種元件其進行不同 Vbase 的脈衝量測,以進一步了解暫態特性,如圖 12(b) 所示。對於 Diode-8,在量測中有 90% 的時間都是對元件施加 Vbase 的偏壓,因此隨著 Vbase 越大,代表元件產生越多的熱,元件溫度隨之提升,使得在 Vbase 大於 3 V 時開態電流快速增加;然而對於 Diode-2 及 Diode-6,超過 3 V 後開態電流有逐漸下降,推測可能跟缺陷、載子捕獲有關。整體而言,同質 PN 二極體在暫態量測的穩定性較異質 PN 二極體高。

- 3. 可靠度測試與比較:由先前脈衝量測發現在大 Vbase 下 Diode-2 與 Diode-6 有元件劣化之

現象,因此利用長時間的應力測試 (stress),一樣對異質二極體 800 °C/1000 °C 退火樣品 (Diode-6/Diode-8) 及同質二極體 (Diode-2) 三種樣品進行可靠度量測,元件分別會進行 +3 V 與 +10 V 的 1000 秒應力測試,並且在測試前與經過 1 秒、10 秒、100 秒、1000 秒後 進行直流 I-V 量測。整體而言,在 10 V 的 Stress 下元件特性 (開態電流/開啟電壓) 有明顯 變化,如圖 12(d)、(f),Diode-8 因元件電流最大,受熱累積的影響大,因此開態電流在 Stress 後大幅提升 22.7%,與圖 12(a)(b) 脈衝量測結果吻合;Diode-6 在 Stress 後電流降低 28.6%,開啟電壓增加 2.233 V,表示載子捕獲現象嚴重,異質介面與 NiO 品質不如 1000 °C 退火樣品,與圖 12(b) 脈衝量測結果吻合;Diode-2 在 10 V 的 Stress下,不論開態電流 或開啟電壓的變化量皆最少,表示同質二極體的可靠度最佳。

#### Duty cycle = Pulse width / Period

圖 11. 脈衝量測波形示意圖。

圖 12. (a) 不同 Duty cycle、(b) 不同  $V_{base}$  脈衝量測 下開態電流與 DC 模式下開態電流之比值的整理圖、元件在 (c)  $V_{stress}=3$  V、(d)  $V_{stress}=10$  V 下之 Stress 時間與開態電流的關係圖、元件在 (e)  $V_{stress}=3$  V、(f)  $V_{stress}=10$  V 下之 Stress 時間與開啟電壓的關係圖。

# 三、總結

本研究首度以磷離子佈植結合高溫退火與再成長技術,實現電阻率  $1.01~\Omega \cdot cm$  之 P 型  $\beta$ - $Ga_2O_3$ ,相較於未摻雜之氧化鎵,電阻率下降約 9 個數量級。而後製作崩潰電壓 979~V 的 N-side-up 同質 PN 二極體,因其同質接面無應力、晶格不匹配等問題,且氧化鎵的能隙與熱穩定性皆高於氧化鎳 (NiO),展現優異的可靠度及穩定性。另比較 P-side-up 同質 PN 因退火後 Si 擴散漏電偏高,整流特性不佳。本研究突破  $\beta$ - $Ga_2O_3$  長期無 P 型之困境,並提供磷摻雜製程參數與可靠度評估路徑,為高性能氧化鎵功率元件奠定基礎。

### 誌謝

感謝國科會 (計畫編號 113-2221-E-A49-052-MY3)、教育部 UAAT-UIUC 與 UAAT-TAM、力晶積成電子製造股份有限公司與閩康科技經費補助。

#### 參考文獻

- 1. 本文章內容主要來自 蔡欣穎.2024. P型氧化鎵磊晶膜及功率二極體應用之研究. 國立陽明交通大學電子研究所碩 十論文.

- 2. M. Mohamed et al., Journal of Physics: Conference Series, 286, 012027, (2011).

- 3. Jincheng Zhang, Pengfei Dong, Kui Dang, Yanni Zhang, Qinglong Yan, Hu Xiang, Jie Su, Zhihong Liu, Mengwei Si, Jiacheng Gao, Moufu Kong, Hong Zhou & Yue Hao, *Nature Communications*, **13** (1), 3900 (2022).

- 4. H. Altuntas, I. Donmez, C. Ozgit-Akgun, and N. Biyikli, Journal of Alloys and Compounds, 593, 190 (2014).

- 5. M. Baldini, Z. Galazka, and G. Wagner, Materials Science in Semiconductor Processing, 78, 132 (2018).

- 6. M. A. Mastro, A. Kuramata, J. Calkins, J. Kim, F. Ren, and S. J. Pearton, ECS Journal of Solid State Science and Technology, 6 (5), 356 (2017).

- 7. An-Chen Liu, Chi-Hsiang Hsieh, Catherine Langpoklakpam, Konthoujam James, SinghWen-Chung Lee, Yi-Kai Hsiao, Ray-Hua Horng, Hao-Chung Kuo, Chang-Ching Tu, *ACS Omega*, **7** (41), 36070 (2022).

- 8. Gregg Jessen, Kelson Chabak, Andy Green, Jonathan McCandless, Steve Tetlak, Kevin Leedy, "Toward realization of Ga<sub>2</sub>O<sub>3</sub> for power electronics applications," 75th Annual Device Research Conference (DRC), South Bend, IN, USA, June 25-28, (2017).

- 9. M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui, and S. Yamakoshi, Physica. Status Solidi A, 211 (1), 21 (2014).

- 10. Hui Li, Shuo-Huang Yuan, Tsun-Min Huang, Hsuan-Jen Chen, Fu-Hsing Lu, Sam Zhang, Dong-Sing Wuu, *Journal of Alloys and Compounds*, **823**, 153755 (2020).

- 11. Katie R. Gann, Naomi Pieczulewski, Cameron A. Gorsak, Karen Heinselman, Thaddeus J. Asel, Brenton A. Noesges, Kathleen T. Smith, Daniel M. Dryden, Huili Grace Xing, Hari P. Nair, David Michael O. Thompson, *Journal of Applied Physics*, 135 (1), 015302 (2024).

- 12. Kunihiro Suzuki, Yoko Tada, Yuji Kataoka, Kazuo Kawamura, Tsutomu Nagayama, Susumu Nagayama, *IEEE Trans. Electron Devices*, **54** (8), 1985 (2007).

- 13. Ribhu Sharma, Mark E. Law, Fan Ren, Alexander Y. Polyakov, Stephen J. Pearton, *Journal of Vacuum Science & Technology A*, **39** (6), 060801 (2021).

- 14. Congcong Ma, Zhengyuan Wu, Zhuoxun Jiang, Ying Chen, Wei Ruan, Hao Zhang, Heyuan Zhu, Guoqi Zhang, Junyong Kang, Tong-Yi Zhang, Junhao Chub and Zhilai Fang, *Journal of Materials Chemistry C*, **10** (19), 6673 (2022).

- A. Y. Polyakov, N. B. Smirnov, V. Schemerov, A. V. Chernykh, E. B. Yakimov, A. I. Kochkova, A. N. Tereshchenko, and S. J. Pearton, ECS Journal of Solid State Science and Technology, 8 (7) Q3091 (2019).

- Leila Ghadbeigi, Rujun Sun, Jani Jesenovec, Arkka Bhattacharyya, John McCloy, Sriram Krishnamoorthy, Michael A. Scarpulla, Berardi Sensale-Rodriguez, *Journal of Applied Physics*, 131 (8), 085102 (2022).

- 17. K. Sasaki, A. Kuramata, T. Masui, E. G. Villora, K. Shimamura, and S. Yamakoshi, *Applied Physics Express*, 5 (3), 035502 (2012).

- 18. Jianguo Zhang, Wei Wang, Simiao Wu, Zhiming Geng, Jinfu Zhang, Li Chen, Ningtao Liu, Xuejun Yan, Wenrui Zhang, Jichun Ye, *Journal of Alloys and Compounds*, **935**, 168123 (2023).

- 19. M. Higashiwaki, AAPPS Bulletin, 32 (1), 3 (2022).

- 20. Hitoshi Takane1, Yuji Ando, Hidemasa Takahashi, Ryutaro Makisako, Hikaru Ikeda, Tetsuzo Ueda, Jun Suda, Katsuhisa Tanaka1, Shizuo Fujita, and Hidetaka Sugaya, *Applied Physics Express*, **16** (8), 081004 (2023).

- 21. Ray Hua Horng, Xin-Ying Tsai, Fu-Gow Tarntair, Jia-Min Shieh, Shao-Hui Hsu, Jitendra Pratap Singh, Guan-Cheng Su, Po-Liang Liu, *Materials Today Advances*, **20**, (2023).

- 22. Chih-Yang Huang, Xin-Ying Tsai, Fu-Gow Tarntair, Catherine Langpoklakpam, Thien Sao Ngo, Pei-Jung Wang, Yu-Cheng Kao, Yi-Kai Hsiao, Niall Tumilty, Hao-Chung Kuo, Tian-Li Wu, Ching-Lien Hsiao, Ray-Hua Horng, *Materials Today Advances*, 22, (2024).

#### 作者簡介

蔡欣穎先生為國立陽明交通大學電子研究所碩士,現為台積電工程師。

Xin-Ying Tsai received his M.S. from the Institute of Electronics of National Chiao Tung University. He is currently an Engineer of Taiwan Semiconductor Manufacturing Company, Ltd.

李承翰先生現為國立陽明交通大學前瞻半導體研究所博士生。

Cheng-Han Lee is currently a Ph.D. student at the Institute of Pioneer Semiconductor Innovation of National Chiao Tung University.

洪瑞華女士為國立中山大學電機工程研究所博士,現為國立陽明交通大學電子研究所講座教授。

Ray-Hua Horng received her Ph.D. in the Department of Electrical Engineering from National Sun Yat-Sen University. She is currently a Chair Professor at the Institute of Electronics of National Chiao Tung University.