# 氮化鎵基金氧半高電子遷移率電 晶體及積體電路的製作及特性研 究

Investigation of Fabrication and Characteristics of GaN-based Metal-oxide-semiconductor High-electron Mobility Transistors and Integrated Circuits

李清庭 Ching-Ting Lee

利用創新的低溫氣相冷凝系統及光電化學氧化/蝕刻系統製作高性能的空乏型及增強型 氮化鎵基金氧半高速電子遷移率場效電晶體,並整合此兩種型態的電晶體完成互補式金氧半 場效電晶體積體電路,並將其應於共源極反相器電路。實現以氧化鎵基系列的材料完成高功 率及高頻金氧半高速電子遷移率場效電晶體開發,並將其應用於數位邏輯電路中。

The novel vapor cooling condensation system and the photoelectrochemical oxidation/etching systems were used to fabricate high performance depletion mode and enhancement mode gallium nitride (GaN)-based metal-oxide-semiconductor high-electron mobility transistors (MOSHEMTs). The complementary MOSHEMT integrated circuits were fabricated by monolithically integrated the depletion mode and enhancement mode devices and applied in inverter circuits. In this work, high-power and high frequency MOSHEMTs were realized by using the GaN-based semiconductors and used in logic circuits.

# 一、氮化鎵基高電子遷移率電晶體簡介

氮化鎵半導體 (GaN) 是一直接寬能隙半導體,其能隙約為 3.4 eV,相較於傳統的矽半導體 (Si),氮化鎵擁有極高的臨界電場 (約 3.3 MV/cm),以致其所製造的元件能在高溫及高電壓操作而不致崩潰<sup>(1)</sup>。此外,氮化鎵基半導體具有高電子飽和漂移速率 (約為 2.5×10<sup>7</sup> cm/s),其有助於提高元件的高頻性能<sup>(1)</sup>。此外,氮化鎵基半導體具有高電子遷移率 (室溫下約

1500-2000 cm²/V·s),因此可以進一步降低元件的導通電阻來提高元件的輸出功率<sup>(2)</sup>。整體而言,因為氮化鎵半導體具有寬能隙、高飽和速率、高崩潰電場等特性,因此展現出在高功率及高頻應用上的巨大潛力。基於上述的優異特點,因此氮化鎵基半導體已經廣泛地應用於日常生活的照明及顯示器的發光二極體 (light-emitting diodes, LEDs) 中,亦被製作成高電子遷移率電晶體 (high-electron mobility transistors, HEMTs),並成功地應用在 5G 行動通訊基地台、智能手機及平板電腦與電動汽車充電器、資料中心電源及雷達發射/接收模組、太陽能微型逆變器及醫療成像設備等高頻與功率電子中,如圖 1 所示。

圖 1. 氮化鎵基元件的應用。

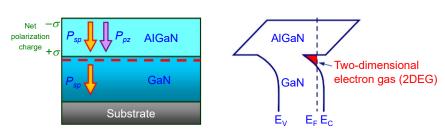

氮化鎵基高電子遷移率電晶體通常採用氮化鋁鎵/氮化鎵 (AlGaN/GaN) 異質結構作為電晶體的載子通道,主要是由氮化鋁鎵與氮化鎵間的自發極化與壓電極化效應在界面處自然形成高密度的二維電子氣 (two-dimensional electron gas, 2DEG),如圖 2 所示,因此二維電子氣無需外界摻雜即可產生,故在室溫下其遷移率可達~2000 cm²/V·s,由此高密度及高遷移率的二維電子氣提供氮化鎵基高電子遷移率電晶體的優異導電通道,因此可以實現大電流和低導通阻抗的元件特性。氮化鎵基高電子遷移率電晶體的高頻性能亦非常突出,其展現出優良的最大振盪頻率 fmax (可達數百 GHz)<sup>(3)</sup>。綜合而言,氮化鋁鎵/氮化鎵異質結構帶來的高濃度二維電子氣是氮化鎵基高電子遷移率電晶體優異性能的核心,使其兼具高功率、高頻與高溫工作能力及功能。

圖 2. 氮化鋁鎵/氮化鎵異質結構之二維電子氣產生示意圖。

## 二、氮化鋁鎵/氮化鎵金氧半高電子遷移率電晶體的製作與特性分析

雖然蕭特基結構 (Schottky structure) 之氮化鋁鎵/氮化鎵金半高電子遷移率電晶體 (AlGaN/GaN MESHEMTs) 得到高度重視且應用於諸多領域,但隨著高性能系統應用的需求,對元件電性表現的要求也與日俱增,在傳統蕭特基結構的金半電晶體中,其元件特性會受限於由金屬與半導體接觸所形成的低位能障壁及界面缺陷的蕭特基結構,因此會引起高閘極漏電流及低崩潰電場等不可避免的問題,因此為提高元件於高頻、低雜訊及高功率系統的應用,在氮化鋁鎵及金屬閘極中置入氧化層,開發氮化鋁鎵/氮化鎵金氧半高電子遷移率電晶體 (AlGaN/GaN metal-oxide-semiconductor high-electron mobility transistors, MOSHEMTs),並依其電晶體的操作型態可分為空乏型 (depletion mode, D-mode) 及增強型 (enhancement mode, E-mode) 金氧半高電子遷移率電晶體,本文分別針對空乏型及增強型介紹幾種不同閘極絕緣層之金氧半高電子遷移率電晶體的特性,並將空乏型及增強型電晶體整合完成製作互補式金氧半積體電路 (complementary metal-oxide-semiconductor integrated circuits),應用於共源極反相器電路,並對其特性進行分析探討。

## 1. 不同閘極氧化層之空乏型氮化鋁鎵/氮化鎵金氧半高電子遷移率電晶體

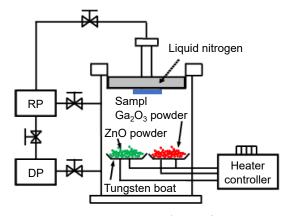

在製作金氧半電晶體的閘極氧化層需具備有高絕緣性、高崩潰電場、高化學穩定性及低接面缺陷等特性,在諸多的應用閘極氧化層薄膜中,其中以金屬氧化物如氧化鋅 (ZnO) 及氧化鎵 (Ga<sub>2</sub>O<sub>3</sub>) 薄膜備受矚目,究其原因為寬能隙氧化鋅介電材料與氮化鎵基半導體皆為纖鋅礦結構,兩者具有幾乎相同的晶格常數,匹配的晶格結構可以有效地降低界面缺陷,然而在大多數的沉積方式下,氧化鋅內存在一定數量的氧空缺及鋅間隙,因此使其呈現一種具導電性的 n 型材料;此外,氧化鋅介電材料具高抗輻射性、高崩潰電場、高介電係數及高化學穩定性等優勢,但仍然與氧化鋅薄膜存在有相同問題,在多數研究利用濺鍍、脈衝雷射沉積、原子層沉積及化學氣相沉積時,由於氧空缺和缺陷的存在,沉積之氧化鎵薄膜多為 n 型薄膜,然而具導電性的 n 型薄膜並不適合作為閘極氧化層。因此本實驗室成功開發一種低成本的低溫氣相冷凝系統 (vapor cooling condensation system),該系統示意圖如圖 3 所示,在此系統中,將樣品置於利用液態氮冷卻的夾具上,並將所欲蒸鍍的氧化鋅粉末及氧化鎵粉末分別置於鎢鉗鍋中,加熱鎢鉗鍋使粉末揮發,此揮發的氧化鋅或氧化鎵材料將蒸鍍於樣品,此樣品受液態氦冷卻,所以此揮發的材料於鍍上樣品時會突然受快速冷卻,此現象猶如鐵匠打鐵

圖 3. 低溫氣相冷凝系統示意圖。

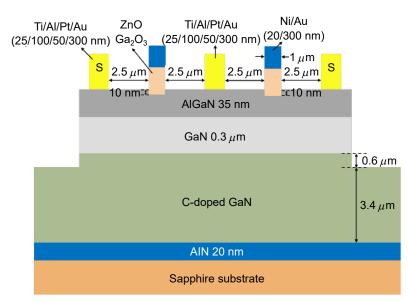

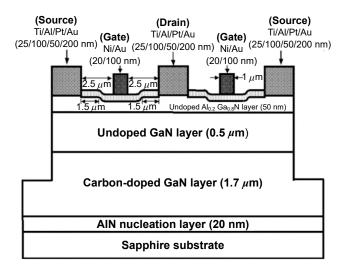

時,將鐵放入高溫鍛燒再突然放入水中冷卻的效果,除可以避免蒸鍍於樣品上的氧化鋅或氧化鎵中的氧再輻射而產生氧缺陷,其氧缺陷低於 1×10<sup>15</sup> cm<sup>-3</sup>,因此具有高絕緣特性適於作為閘極氧化層,基於先前發表之研究發現利用低溫氣相冷凝系統在約 80 K 的低溫下沉積的氧化鋅薄膜及氧化鎵薄膜可以有效的抑制氧空缺及缺陷<sup>(4)</sup>,且已將其應用於氮化鎵異質結構發光二極體<sup>(5)</sup>。本研究使用低溫氣相冷凝系統成長出高品質及低缺陷之氧化鋅<sup>(6,7)</sup> 和氧化鎵薄膜<sup>(8)</sup> 作為氮化鋁鎵/氦化鎵金氧半高電子遷移率電晶體的閘極氧化層,其示意圖如圖 4 所示,其在低雜訊及高頻特性均呈現優良的特性成果<sup>(6-8)</sup>。

圖 4. 具氧化鋅或氧化鎵閘極氧化層之氮化鋁鎵/氮化鎵金氧半 高電子遷移率電晶體結構示意圖<sup>(6-8)</sup>。

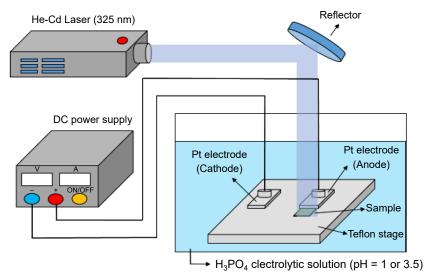

電子元件的缺陷及界面狀況對於元件的特性均有重大的影響,其來源有分別由元件磊晶層結構及製程所造成者,因此為提升電子元件的功能,必須優化磊晶層的設計及成長磊晶條件,並在製程避免外部的汙染及界面缺陷,此外,為提高電子元件的崩潰電壓以提高輸出功率,因此必須平滑通道的電場分佈,並避免出現突出的電場現象,其一般的解決方法是在閘極下方挖掘適當的深度作為閘極掘入區域 (gate-recessed region),然而在利用電漿製作閘極掘入區域時,氧化鎵基材料會受電漿所衝擊而損壞,此外,在蒸鍍閘極氧化層時,其界面會受外部汙染所影響而提高界面缺陷密度,有見於矽基積體電路的製程優點,在於能夠利用濕式及高溫氧化法直接在矽材料直接成長高品質的二氧化矽氧化層,此直接成長氧化層的方法可以大量降低界面的缺陷密度,因此若有方法能在氦化鎵基半導體上直接成長氧化層,必能有效地降低外部汙染及界面缺陷密度,並可預期提昇電子元件的功能,因此設計及發展光電化學氧化法 (photoelectrochemical oxide method, PEC oxide method) 直接於氦化鋁鎵半導體上生長出高品質低界面缺陷密度的金屬氧化層薄膜(9),其系統架構如圖 5 所示,將氧化鎵基磊晶層樣品置於 PH 值為 3.5 的磷酸溶液中,照射 He-Cd 雷射 (波長為 325 奈米) 於溶液與氦化鎵基材料界面,此雷射的光子能量大於氦化鋁鎵的能隙,因此可以在界面產生電子一電洞對,所產生的電洞將會與氦化鋁鎵產生氧化鎵及氧化鋁混合金屬氧化物層,在 PH 值為 3.5

時,其產生金屬氧化層的速度高於受磷酸溶液溶解的速度,因此可以直接成長金屬氧化物層 作為氮化鋁鎵/氮化鎵金氧半高電子遷移率電晶體的閘極氧化層,採用光輔助電容-電壓量 測法量測電容值,並利用分析計算氧化層與半導體表面的界面態密度,其量測光源是使用波 長為 325 nm 的氙燈進行照射,其界面態密度 ( $D_{it}$ ) 為  $5.1 \times 10^{11} \, \mathrm{eV}^{-1} \mathrm{cm}^{-2}$ ,由量測結果顯示, 光電化學氧化法能夠在氮化鋁鎵半導體上直接成長具有高品質與低界面態密度的氧化層薄膜 (9)。在不破壞氮化鋁鎵/氮化鎵異質結構為前提,使閘極更接近二維電子氣通道,以此提升 閘極控制能力,並使電場分佈更為緩和以提高崩潰電壓,因此利用光電化學蝕刻法進行閘極 掘入製程, 當磷酸溶液的 PH 值為 1 時, 其蝕刻速度高於氧化層成長速度, 因此可以直接製 作閘極掘入區域,並可精確控制掘入深度,具有閘極掘入結構及閘極氧化層之氦化鋁鎵/氦 化鎵金氧半高電子遷移率電晶體示意圖如圖  $6^{(10)}$ ,在直流量測部分,利用光電化學氧化法直 接成長閘極氧化層,比較有無閘極掘入之氮化鋁鎵/氮化鎵空乏型金氧半高電子遷移率電晶 體,研究結果發現以光電化學蝕刻法製作閘極掘入區域及以光電化學氧化法直接成長閘極氧 化層的空乏型電晶體具有優良的低頻雜訊特性及高崩潰電壓特性,因此可以得知原先存在於 試片表面的損傷及缺陷能夠經由光電化學法所製作的閘極掘入去除,進而提升元件低頻雜訊 特性,此外,利用直接成長閘極氧化層亦可如同在矽材料直接成長二氧化矽的功能,提昇金 氧半電子元件的功能。

圖 5. 光電化學氧化/蝕刻系統架構圖。

#### 2. 不同閘極氧化層之增強型氮化鋁鎵/氮化鎵金氧半高電子遷移率電晶體

在實際的積體電路應用中,增強型金氧半高電子遷移率電晶體具有設計簡單與降低多餘功耗等優勢,在互補式金氧半高電子遷移率電晶體 (CMOS HEMTs) 中是不可或缺的元件,過去已有提出多種方法並實現製作氮化鋁鎵/氮化鎵增強型金氧半高電子遷移率電晶體,其中包括有氟化物電漿 (fluoride-based plasma)、閘極掘入、鐵電閘極氧化層 (ferroelectric gate oxide layer) 及 p 型氮化鎵等方法,惟氟化物電漿會導致氮化鋁鎵表面造成嚴重損傷,此外,氟離子在氮化鎵材料中會造成臨界電壓的不穩定,進而增加閘極漏電流及特性不穩定;閘極掘入必須精確控制掘入深度,若蝕刻深度控制不當,可能破壞二維電子氣通道並降低電子遷

圖 6. 具閘極掘入結構及直接成長閘極氧化層之氮化鋁 鎵/氮化鎵金氧半高電子遷移率電晶體結構示意圖<sup>(10)</sup>。

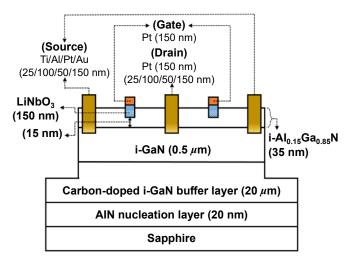

移率或無法完全空乏二維電子氣;鐵電閘極氧化層必須要具有極為優良極化功能,方能完全空乏二維電子氣,利用 p 型氮化鎵則需要相當高的 p 型摻雜濃度,在氮化鋁鎵/氮化鎵金氧半高電子遷移率電晶體的二維電子氣通道是由氮化鋁鎵/氮化鎵異質接面向下方向的極化現象,進而空乏二維電子氣,由於具有 C<sup>+</sup> 範疇 (domain) 的鈮酸鋰 LiNbO<sub>3</sub> 薄膜具有向上方向的極化現象,也於為,因此為改善上述的缺點,研究結合閘極掘入與鐵電閘極氧化層兩種技術,藉由鐵電閘極氧化層的極化方向與氮化鋁鎵/氮化鎵的極化方向相反以空乏一部份的二維電子氣,因此不需要具有高極化的鐵電氧化層,此外,尚未被空乏的二維電子氣則藉由閘極掘入加以空乏,因此不需要精確的控制閘極掘入深度,降低破壞二維電子氣則藉由閘極掘入加以空乏,因此不需要精確的控制閘極掘入深度,降低破壞二維電子氣通道的風險。本研究利用脈衝電射沉積系統 (pulsed laser deposition, PLD) 沉積鈮酸鋰 (LiNbO<sub>3</sub>) 薄膜,並利用在氧氣環境的退火製程將鈮酸鋰薄膜的極化方向轉換成與氧化鋁鎵/氮化鎵完全相反的極化方向,並應用此具有極化特性之鈮酸鋰薄膜作為增強型金氧半高電子遷移率電晶體元件之閘極氧化層,再

圖 7. 單層銀酸鋰閘極氧化層的金氧半高電子遷移率電晶體結構示意圖<sup>(11)</sup>。

結合光電化學蝕刻法進行閘極掘入,圖 7 為具有單層鈮酸鋰閘極氧化層的金氧半高電子遷移率電晶體結構示意圖,整合閘極掘入及鈮酸鋰氧化層的製程,不但可以具有在製程的容忍度,而且可以有效提升元件之臨界電壓及最大轉導,達到高穩定性之增強型金氧半高電子遷移率電晶體<sup>(11)</sup>。結合上述對鈮酸鋰鐵電薄膜的最佳退火溫度 600 °C 及時間 30 分鐘與利用光電化學蝕刻法的最佳掘入蝕刻深度以製作具有閘極掘入之鈮酸鋰閘極氧化層的金氧半高電子遷移率電晶體,並對其進行電性量測及分析,其臨界電壓為 +0.4 V,最大轉導為 56.0 mS/mm,次臨界擺幅 (SS) 為 424.7 mV/decade,在頻率為 10 Hz 的雜訊功率密度約為 8.1×10<sup>-11</sup> Hz<sup>-1</sup>。由實驗結果可知,整合閘極掘入與鈮酸鋰閘極氧化層的製程技術可使臨界電壓正偏移,達到增強型元件操作之目的。

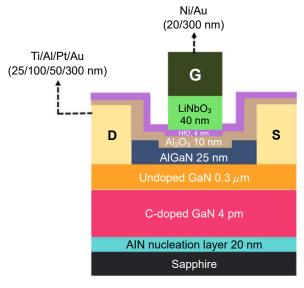

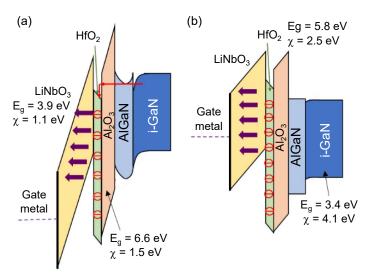

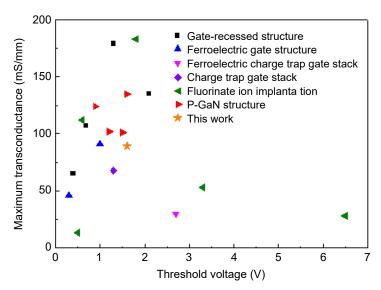

為進一步提升增強型金氧半高電子遷移率電晶體的功能,本研究開發堆疊式閘極氧化 層的結構,圖 8 為具有鈮酸鋰/氧化鉛 (HfO2)/氧化鋁 (Al2O3) 堆疊式閘極氧化層的金氧 半高電子遷移率電晶體之結構示意圖(12),其堆疊式閘極氧化層依序為利用原子層沉積系統 (atomic layer deposition, ALD) 在以光電化學蝕刻法掘入的閘極區域上沉積厚度為 10 奈米的 氧化鋁與厚度為4奈米的氧化鈴薄膜,分別作為電子穿隧層與電荷捕捉層,接著利用脈衝雷 射沉積系統成長最上層的 40 奈米厚度之鈮酸鋰薄膜作為電荷阻擋層。欲使此結構能達成增 強型元件須先進行初始化 (initialization),對閘極施加一正偏壓以吸引二維電子氣通道內部的 電子經氧化鋁穿隧層至氧化鈴電荷捕捉層,藉由此初始化功能空乏二維電子氣通道,圖 9(a) 及 (b) 分別表示初始化時及初始化後的堆疊式闡極氧化層的能帶圖(12)。此具有極化特性的鈮 酸鋰薄膜除可以空乏一部份的二維電子氣以提高臨界電壓外,由於鈮酸鋰薄膜具有高絕緣及 高崩潰電場的特性,並與氧化鉛電荷捕捉層具有異質接面,因此尚可以阻止捕捉在氧化鉛層 的電子流向閘極金屬層,以致除可以降低閘極漏電流外,亦可以使元件之臨界電壓獲得大幅 度之正偏移,以完成更優良的增強型元件功能。由此實驗可得知堆疊式閘極氧化層結構能在 不影響最大轉導值的情況下,有效地將臨界電壓大幅度正偏移完成增強型操作。圖 10 比較 利用各種方法製作增強型氮化鋁鎵/氮化鎵高電子遷移率電晶體的最大轉導與臨界電壓特性 (12) 。

圖 8. 具銀酸鋰/氧化鉿/氧化鋁堆疊式閘極氧化層的金氧半高電子遷移率電晶體結構示意圖<sup>(12)</sup>。

圖 9. 堆疊式閘極氧化層在 (a) 初始化時及 (b) 初始化後的能帶圖(12)。

圖 10. 利用各種方法製作增強型氮化鋁鎵/氮化鎵高電子遷 移率電晶體的特性比較<sup>(12)</sup>。

# 三、互補式氮化鋁鎵/氮化鎵金氧半高電子遷移率電晶體積體電路

隨著摩爾定律的推進,電子元件的微縮已然成為各大廠商研發積體電路的重點,其中又以互補式金氧半場效電晶體 (complementary metal-oxide-semiconductor, CMOS) 為現今積體電路晶片中的核心基本結構。目前互補式金氧半場效電晶體的積體電路廣泛應用於各類數位電路中,例如反相器、中央處理器、記憶體及感測系統等方面。傳統的矽基及 III-V 族基互補式場效電晶體皆以整合 n 型通道及 p 型通道金氧半場效電晶體所製作者,不過隨著低雜訊、高功率及高頻系統應用的需要,氦化鎵憑藉其高電子遷移率、寬能隙與高崩潰電壓等優勢,成為現今製作金氧半場效電晶體及其積體電路的重要半導體材料,然而不易在氦化鎵基材料 摻雜高濃度的 p 型雜質以獲得高電洞濃度,此外,電洞在氦化鎵基材料的遷移率相當低,且

目前尚無法產生二維電洞氣,因此目前製作高品質及高功能 p 型通道金氧半場效電晶體的困難程度相當高,故尚無法製作整合 n 型及 p 型通道的高功能互補式氮化鎵基金氧半場效電晶體結構。本研究整合空乏型與增強型氮化鎵基金氧半高電子遷移率電晶體,利用調控空乏型元件之氮化鋁鎵厚度以達到增強型元件與空乏型元件之電流匹配的互補式氮化鋁鎵/氮化鎵金氧半高電子遷移率電晶體積體電路。

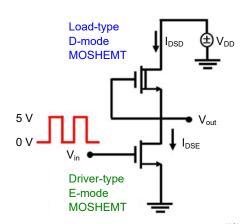

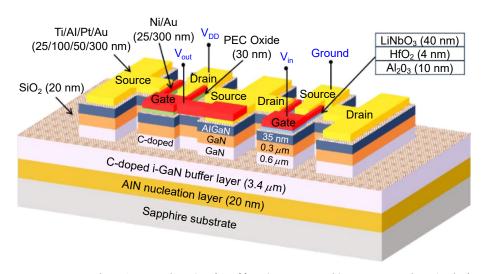

本研究設計之共源極反相器電路,如圖 11 所示,整合空乏型元件作為負載端與增強型 元件作為輸入控制元件(13)。利用空乏型元件對輸出端進行充電,增強型元件則依據輸入電 壓的高低進行導通或關閉,控制輸出端的放電行為,藉此實現輸出隨輸入反相變化的特性, 達到反相器的功能,其中利用堆疊式閘極氧化層及光電化學蝕刻法掘入閘極區域來製作增強 型元件,並搭配光電化學蝕刻法及光電化學氧化法製作空乏型元件,完成增強型與空乏型整 合的互補式金氧半高電子遷移率電晶體的製作,其三維結構示意圖如圖 12 所示,堆疊式閘 極氧化層採用具極化特性的鈮酸鋰鐵電薄膜作為堆疊式閘極氧化層最上層,並搭配中間層的 氧化鉿薄膜作為電子捕捉層以捕捉儲存電子,以及最下層的氧化鋁作為電子穿隧層,使電子 穿隧氧化鋁層並捕捉儲存於氧化鉿層中,進而有效達到空乏二維電子氣通道之目的,同時搭 配光電化學法蝕刻進行閘極掘入結構的製作,可進一步使閘極更接近通道並提升閘極對通道 的控制能力,完成增強型金氧半高電子遷移率電晶體的製作。空乏型金氧半高電子遷移率電 晶體採用光電化學氧化法直接在氮化鋁鎵層生成金屬氧化層,不僅能夠顯著降低氮化鋁鎵與 氧化層之間的界面態密度,亦可改善元件界面品質。相較於以往藉由調整場效電晶體的閘極 寬長比 (W/L) 來控制電流的設計方式,本研究採用光電化學蝕刻法,調控空乏型元件之氮化 鋁鎵厚度,進而精確調整增強型與空乏型元件間的電流比值  $(\beta = I_{DSF}/I_{DSD})$ ,其中  $I_{DSF}$  為增強 型元件汲源極飽和電流,I<sub>DSD</sub> 為空乏型元件汲源極飽和電流,除有助於提升整體電路設計靈 活性與實用性外,尚可以達到最佳的電路特性。

圖 11. 共源極反相器電路結構示意圖(13)。

空乏型元件利用光電化學法蝕刻不同厚度的氮化鋁鎵薄膜,藉此調變電流大小,在剩餘不同厚度之氮化鋁鎵薄膜 ( $12 \text{ nm} \times 10 \text{ nm} \times 8 \text{ nm}$ ) 的空乏型元件進行分析,當閘源極電壓為  $0 \text{ V} \times 30 \text{ Nm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm} \times 32.5 \text{ mm}$  为  $0 \text{ V} \times 30 \text{ mm}$  为  $0 \text{ V} \times 30$

圖 12. 光電化學法與堆疊式閘極薄膜製作氮化鋁鎵/氮化鎵互補式金氧半高電子遷移率電晶體結構示意圖<sup>(13)</sup>。

來改變。對於增強型金氧半高電子遷移率電晶體,在閘源極施加 12 V 並持續 10 ms 的初始 化條件後,當閘源極電壓為 5 V 及汲源極電壓為 5 V 的操作條件下,其汲源極飽和電流達到 260.5 mA/mm,元件臨界電壓為 1.5 V。

由表 1 所示,藉由調整氮化鋁鎵厚度至 12 nm、10 nm、8 nm,可以獲得電流比例由 5 倍、8 倍調整到 22 倍,輸出低電壓  $(V_{OL})$  值分別從 0.45 V 及 0.28 V 下降到 0.10 V,對應靜態功耗從 266 mW 及 164 mW 下降到 69 mW,同時輸出擺幅 (output swing) 由 4.55 V 及 4.72 V 上升至 4.90 V,高雜訊邊際  $(NM_H)$  分別為 1.44 V、1.80 V 與 1.99 V;低雜訊邊際  $(NM_L)$  分別為 1.48 V、1.62 V 與 1.73 V,由進一步利用轉移曲線得知在輸出電壓  $(V_{out})$  為二分之一驅動電壓  $(V_{DD}/2)$  時,所對應之輸入電壓  $(V_{in})$  各為 2.80 V、2.60 V 與 2.49 V,當電流比例為 22 倍時,其輸入電壓已接近 2.5 V,代表此時反相器轉移曲線已達到無偏斜特性。整體而言,光電化學蝕刻法不僅可調變電流比例  $\beta$  值,也有助於實現高效、低功耗的氮化鋁鎵/氮化鎵互補式金氧半高電子遷移率電晶體。

| <b>水1. 火相語制山村江水小門电加比門「                                    </b> |                       |                        |                     |                        |                        |                                      |

|----------------------------------------------------------------|-----------------------|------------------------|---------------------|------------------------|------------------------|--------------------------------------|

|                                                                | Current ratio $\beta$ | V <sub>OL</sub><br>(V) | Output swing<br>(V) | NM <sub>H</sub><br>(V) | NM <sub>L</sub><br>(V) | $V_{in}$ as $V_{out} = V_{DD}/2$ (V) |

|                                                                | 5                     | 0.45                   | 4.55                | 1.44                   | 1.48                   | 2.80                                 |

|                                                                | 8                     | 0.28                   | 4.72                | 1.80                   | 1.62                   | 2.60                                 |

|                                                                | 22                    | 0.10                   | 4.00                | 1.00                   | 1 72                   | 2.40                                 |

表 1. 反相器輸出特性於不同電流比例下數據整理(13)。

## 四、結論

利用創新設計的低溫氣相冷凝系統製備高品質的金屬氧化薄膜如氧化鋅及氧化鎵薄膜作為閘極氧化層,利用光電化學蝕刻法製作閘極掘入區域,並利用光電化學氧化法直接於氮化鋁鎵表面成長高品質氧化層作為空乏型氮化鋁鎵/氮化鎵金氧半高電子移動率場效電晶體的

間極氧化層,由此等製程所製作的空乏型金氧半場效電晶體均具有良好的直流與交流特性。 在增強型氮化鋁鎵/氮化鎵金氧半高電子移動率場效電晶體的開發部分,利用光電化學蝕刻 法先直接蝕刻部分的氮化鋁鎵,使其達到間極掘入的效果,再利用原子層沉積系統依序沉積 氧化鋁及氧化鉿薄膜作為電子穿隧層與電荷捕捉層,接著利用脈衝雷射沉積系統在其上成長 具有極化的鈮酸鋰薄膜作為電荷阻擋層,利用此堆疊式閘極氧化層可以製作具有優良直流、 交流與低雜訊特性的增強型氮化鋁鎵/氮化鎵金氧半高電子移動率場效電晶體。此外,亦將 所開發的空乏型與增強型氮化鋁鎵/氮化鎵金氧半高電子移動率場效電晶體的技術整合完成 互補式金氧半積體電路之開發,由此所設計及製作的共源極反相器具有優良的控制特性及功 能。

## 參考文獻

- 1. C. Langpoklakpam, Y. K. Hsiao, E. Y. Chang, C. H. Lin, and H. C. Kuo, Solid-State Electronics, 216, 108930 (2024).

- 2. F. Yang, C. Xu, and B. Akin, IEEE Trans. Power Electronics, 34, 10121 (2019).

- 3. P. Cui and Y. P. Zeng, Sci. Rep., 12, 16683 (2022).

- 4. H. Y. Lee, S. D. Xia, W. P. Zhang, L. R. Lou, J. T. Yan and C. T. Lee, Journal of Applied Physics, 108, 073119 (2010).

- 5. R. W. Chuang, R. X. Wu, L. W. Lai and C. T. Lee, Applied Physics Letters, 91, 231113 (2007).

- 6. C. T. Lee, Y. L. Chiou and C. S. Lee, IEEE Electron Device Letters, 31, 1220 (2010).

- 7. Y. L. Chiou, C. S. Lee, and C. T. Lee, Applied Physics Letters, 97, 032107, (2010).

- 8. H. Y. Lee, T. W. Chang and C. T. Lee, Journal of Electronic Materials, 50, 3748 (2021).

- 9. L. H. Huang, and C. T. Lee, Journal of The Electrochemical Society, 154, H862 (2007).

- 10. Y. L. Chiou, L. H. Huang, and C. T. Lee, IEEE Electron Device Letters, 31, 183 (2010).

- 11. C. T. Lee, C. L. Yang, C. Y. Tseng, J. H. Chang, and R. H. Horng, *IEEE Transactions on Electron Devices*, **62**, 2481 (2015).

- 12. H. Y. Lee, C. H. Lin, C. C. Wei, J. C. Yang, E. Y. Chang, and C. T. Lee, *IEEE Transactions on Electron Devices*, **68**, 3768 (2021).

- 13. H. J. Hsieh, H. Y. Lee, C. T. Lee, Materials Science in Semiconductor Processing, 169, 107908 (2024).

#### 作者簡介

李清庭先生為美國卡內基美隆大學電機工程博士,現為成功大學及元智大學名譽講座教授。

Ching-Ting Lee received his Ph.D. from the Electrical Engineering Department of the Carnegie-Mellon University, Pittsburgh, PA, USA. He is the Emeritus Chair Professor at the National Cheng Kung University and Yuan Ze University.