# 新穎準二維半導體製備與特性調控

## Fabrication and Engineering of Novel Quasi Two-dimensional Semiconductors

陳怡誠、王詠鈞、朱英豪

Yi-Cheng Chen, Yong-Jyun Wang, Ying-Hao Chu

隨著現代微電子技術的快速發展，矽因其適中的能隙、穩定的物理與化學性質，以及與高品質原生氧化層的界面特性，長期以來一直是半導體元件的核心材料，然而，當製程節點縮小至 10 奈米以下，矽材料逐漸面臨諸如載子遷移率下降、短通道效應與界面缺陷等挑戰，促使研究人員積極尋求具備高性能與新穎物理特性的替代材料，其中，準二維半導體  $\text{Bi}_2\text{O}_2\text{Se}$  因其高電子遷移率、環境穩定性及可自發生成高介電常數原生氧化層  $\text{Bi}_2\text{SeO}_5$ ，在次世代元件中展現極大潛力， $\text{Bi}_2\text{O}_2\text{Se}$  可透過多種製程方法合成，如化學氣相沉積 (chemical vapor deposition, CVD)、分子束磊晶 (molecular beam epitaxy, MBE) 與脈衝雷射沉積 (pulsed laser deposition, PLD)，並能實現異質整合與極限尺寸電晶體架構 (如鰭式場效電晶體 (fin field-effect transistor, FinFET) 與環繞閘極場效電晶體 (gate all around field effect transistor, GAAFET))，此外，其材料本身亦具備鐵電性、熱電性與量子效應等多樣物理特性，使其在邏輯、記憶、感測與能源元件中具備應用潛力，本文探討  $\text{Bi}_2\text{O}_2\text{Se}$  於材料成長、元件整合與特性調控的可行性與發展。

With the rapid advancement of modern microelectronics, silicon has long served as the core material for semiconductor devices due to its moderate bandgap, stable physical and chemical properties, and high-quality interface with its native oxide layer. However, as process node scales down to below 10 nm, silicon increasingly faces challenges such as reduced carrier mobility, short-channel effects, and interface defects. This has driven researchers to actively seek alternative materials with superior performance and novel physical properties. Among them, quasi-two-dimensional semiconductor  $\text{Bi}_2\text{O}_2\text{Se}$  has shown great potential for next-generation devices, owing to its high electron mobility, environmental stability, and ability to spontaneously form a high-k native oxide layer ( $\text{Bi}_2\text{SeO}_5$ ).  $\text{Bi}_2\text{O}_2\text{Se}$  can be synthesized using various fabrication techniques, including chemical vapor deposition (CVD), molecular beam epitaxy (MBE), and pulsed laser deposition (PLD), and can be integrated into advanced transistor architectures. Furthermore, the material exhibits diverse physical properties, making it a promising candidate for applications in logic, memory, sensing, and energy devices. This article explores the development and research prospects of  $\text{Bi}_2\text{O}_2\text{Se}$  in material growth, device integration, and property engineering.

## 一、簡介

矽自 1950 年代末積體電路 (integrated circuit, IC) 問世以來，一直是主導微電子領域的半導體材料，主要是因為其適中的能隙 (約 1.1 eV)、優異的化學穩定性，以及在地殼中的豐富含量，這些特性使得矽能夠承載複雜的製程並推動半導體產業的持續發展，此外，矽的原生氧化物 (二氧化矽) 不僅能作為保護層使矽免於污染，也因其介電特性以及與矽之間優異的介面品質，而被大量運用在矽基場效電晶體 (field-effect transistor, FET) 中的閘極介電層，然而，隨著摩爾定律的推進，當 IC 尺寸縮小至 10 奈米以下節點時，矽基製程面臨多項挑戰，如界面缺陷、短通道效應、載子遷移率下降與厚度不均等問題，因此，為了延續摩爾定律，研究人員投入大量的資源探索新穎半導體材料，包含：矽鍺 (SiGe)、鍺 (Ge)、III-V 族半導體、氧化物半導體以及二維材料 (2D materials) 等，其中原子級厚度的二維材料出現，為探索奈米尺度的低維物理及設計創新功能元件開啟了全新的平台，早期研究主要集中於「經典」二維材料，例如石墨烯、過渡金屬二硫族化合物 (TMDs，如  $\text{MoS}_2$  和  $\text{WS}_2$ )、黑磷、拓撲絕緣體(如  $\text{Bi}_2\text{Se}_3$  和  $\text{Bi}_2\text{Te}_3$ )，以及單層元素 (矽烯、錫烯、鍺烯、鎢烯和砷烯) 等，這些層狀材料可被視為本質二維材料，因為其相鄰層間的作用力是弱的凡德瓦力 (van der Waals force, vdW)，而非強共價鍵，因此層與層之間形成了凡德瓦爾間隙，另一類層狀材料則是由帶有正電或負電的原子層組成，這些層由具電荷的陽離子或陰離子隔開，因此，這些層是由弱的靜電作用力維繫，並可被定義為層狀準二維 (quasi-2D) 材料，然而，這些材料不像矽一樣具有高穩定的原生氧化層，使其難以撼動矽的主導地位，儘管已有許多研究致力於改善氧化層，但相較於矽／二氧化矽的界面，這些材料的氧化層往往具有非化學計量比與高度缺陷，為尋找可行替代材料，自 2017 年以來，科學家發現了一種具備高電子遷移率且具空氣穩定性的準二維半導體-  $\text{Bi}_2\text{O}_2\text{Se}$  (BOSe)。

BOSe 為正方晶 (tetragonal) 結構 ( $a = b = 3.891 \text{ \AA}$ ， $c = 12.213 \text{ \AA}$ )，因其有趣的基礎物理性質及在元件應用上的表現而受到矚目，BOSe 可透過多種製程方法製備低維度材料，包括化學氣相沉積、分子束磊晶、脈衝雷射沉積，以及溶液輔助法，這些多樣的合成方法，結合 BOSe 高度對稱的晶體結構，使得研究人員能夠獲得各種形貌的材料，例如在雲母上的凡德瓦磊晶、生長在氧化物單晶  $\text{SrTiO}_3$  上磊晶，以及在  $\text{SiO}_2$  的多晶沉積和自支撐二維晶體，除優異的電子特性外，BOSe 經由熱氧化、紫外輔助插層氧化與氧電漿氧化等方式可形成原生氧化層  $\text{Bi}_2\text{SeO}_5$  (BSO)，其具有原子級平坦的介面，BSO 具備高介電常數 ( $\epsilon = 15 - 20$ )，可作為理想的閘極介電層應用於 BOSe/BSO 自組裝場效電晶體中，BOSe 擁有獨特的缺陷結構，在低溫 1.9 K 下，載子遷移率可達約  $28,900 \text{ cm}^2/\text{Vs}$  在室溫下遷移率約為  $450 \text{ cm}^2/\text{Vs}$ ，以及優異的次臨界擺幅 ( $\text{SS} \sim 65 \text{ mV/dec}$ ) 利用這個特性，科學家已經能利用這個材料開發出超越矽基的次世代半導體元件。

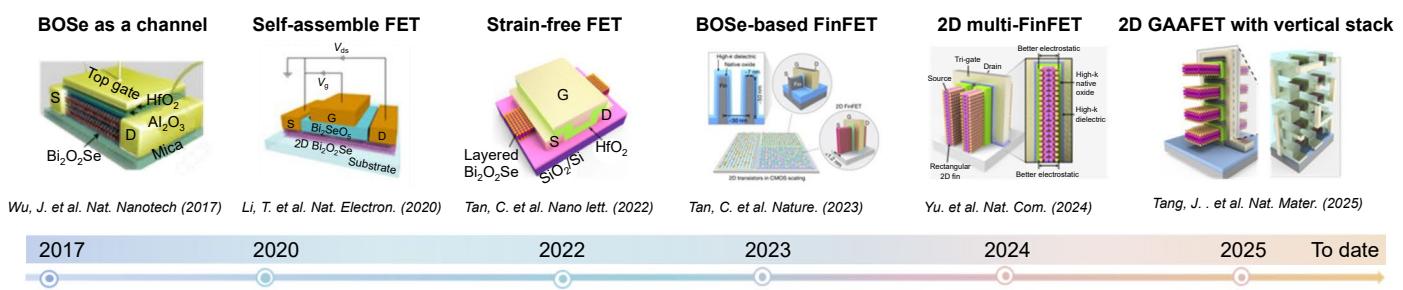

利用 BOSe/BSO 系統的獨特優勢，研究人員已成功開發出多種先進電晶體架構 (圖 1)：(1) 鰭式場效電晶體：相關研究已實現有效的鰭狀通道長度縮至 1.8 nm 的 3D FinFET<sup>(1)</sup>，近期更透過磊晶技術，利用絕緣基板上的原子級階梯來控制 BOSe 鰭狀結構的成核位置與平面上的軸向，成功製備出高密度、單一軸向的二維 BOSe 多鰭場效電晶體 (multi-FinFET)<sup>(2)</sup>，這種基於磊晶整合的 BOSe/BSO 鰭－氧化層異質結構所製作的 2D multi-FET，展現出高效能與優異的元件穩定性，透過離子束蝕刻等技術，預期可藉由改善基板階梯結構，實現更高階、有序排列的 BOSe 鰭狀陣列；(2) 環繞式閘極場效電晶體：透過磊晶單晶三維

整合 (M3D) 技術，可將 BOSe/BSO 系統與多層石墨烯等材料交替堆疊應用於多層堆疊的 GAAFET 結構<sup>(3)</sup>，突破了矽基技術在功耗微縮上的限制，透過原子級平坦介面與超薄的等效氧化層厚度 (equivalent oxide thickness, EOT)，所製備的 2D BOSe/BSO GAAFET 展現出優異的閘極控制效率、優異的電性表現以及元件穩定性。

此外 BOSe 材料本身的高載子遷移率，使得該系統中具有多種新穎物理現象，例如磁阻效應、強烈的量子振盪 (shubnikov-de haas effect, SdH) 以及強烈的自旋軌道耦合，除了特殊的電子與電荷傳輸特性外，BOSe 還具有多種功能以及物理特性，例如鐵電性<sup>(4)</sup>、鐵彈性<sup>(5)</sup> 及熱電性<sup>(6)</sup>，因此，BOSe 在電子學、光電子學、感測器及能源技術等領域展現出強大的應用潛力。

圖 1. 準二維 BOSe 特性與發展<sup>(1-3, 7-10)</sup>。

## 二、研究成果

### 2.1 製備 BOSe 薄膜

在先進電子與光學領域中，對材料的尺寸、厚度與晶體品質有著極高的要求，因此，材料的合成往往是研究後續材料特性的第一步，在不同的應用需求中，研究人員提出了各種合成方式來成長高品質且具高結晶性 BOSe，包括化學氣相沉積<sup>(11)</sup>、分子束磊晶<sup>(12)</sup>、機械剝離<sup>(13)</sup> 以及脈衝雷射沉積<sup>(14)</sup>，此外，由不同合成方法製得的材料在結構與性質上會存在差異，在二維材料的成長過程中，選擇適當的基板是一個關鍵步驟，BOSe 具有獨特的層狀結構與強的鍵結特性以及層間靜電作用力，這些特性使得在氣相沉積過程中能夠製備出超薄的 BOSe 層，尤其是雲母基板因其化學惰性，且與 BOSe 之間有相對較弱的相互作用，成為 BOSe 成長的一個平台，這使得可以精確控制 BOSe 在雲母上沿著 [001] 晶軸方向的自組裝成長，然而，BOSe 與雲母 [001] 面存在晶格不匹配，導致合成出的 BOSe 晶體在內平面方向上呈隨機軸向排列，而  $\text{SrTiO}_3$  ( $a = b = 3.905 \text{ \AA}$ ) 則與 BOSe 有極佳的晶格匹配為高品質、大面積 BOSe 薄膜的生長提供了良好的成長平台，最常使用的是化學氣相沉積是一種控制氣相反應在基板表面沉積薄膜的製程，具有高形貌與結晶性可控性，因此廣泛應用於大面積高品質二維材料的製備，由於 BOSe 的層狀結構，在化學氣相沉積成長過程中易形成超薄且側向尺寸大的二維晶體，常用的前驅物為高純度的  $\text{Bi}_2\text{O}_3$  與  $\text{Bi}_2\text{Se}_3$ ，成長機制主要包括前驅物的蒸發、氣相傳輸與在基板表面的沉積，在部分條件下，還需引入氧氣以進一步控制膜層的厚度與組成，確保薄膜品質與穩定性。

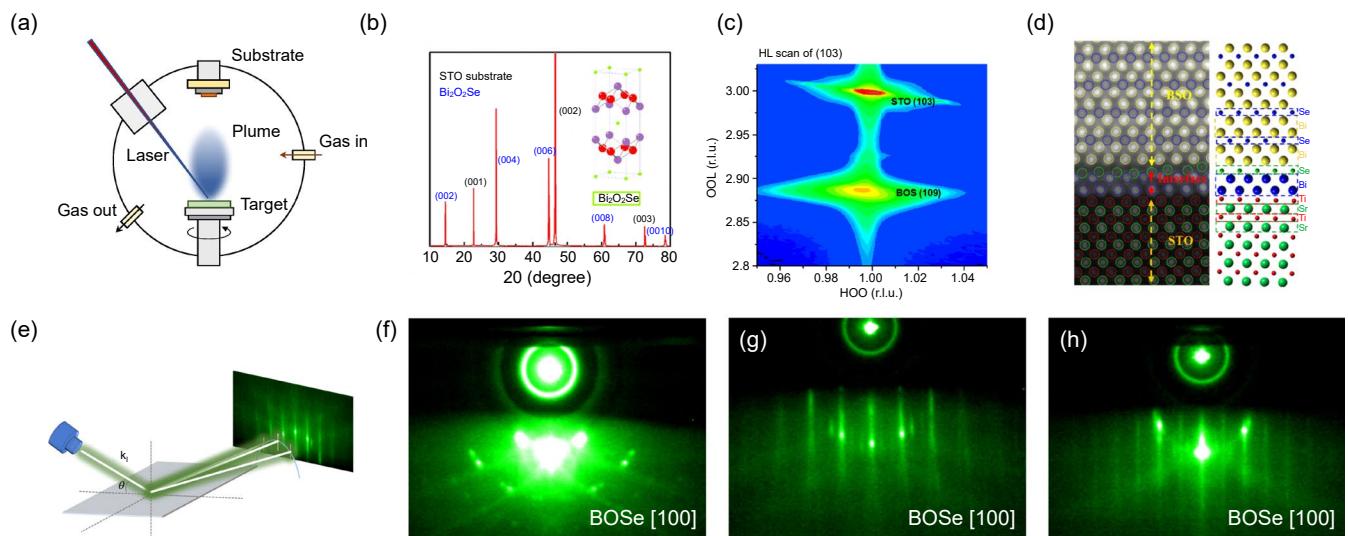

本研究採用脈衝雷射沉積法成長高品質的 BOSe 薄膜，脈衝雷射沉積法是一種用於開發特定組成之先進材料的技術 (圖 2(A))，可用於快速驗證該材料是否可以合成與應用，利用

脈衝雷射轟擊靶材，可精確地將材料轉移至薄膜中，雷射剝蝕是一種基於雷射光與材料之間強烈交互作用的技術，能以化學計量比準確地轉移材料組成，具有沉積速率快、可成長高品質晶體薄膜、成分轉移準確，並且能成長各類複雜材料等優勢，可以在單一腔體內，製備多層結構，且脈衝雷射沉積法成長速率約為化學氣相沉積的十倍，為製備 BOSe 元件開發提供一個有效平台，本研究利用脈衝雷射沉積法成功開發出 BOSe 薄膜，X 光繞射 (X-ray diffractometer, XRD) 技術驗證磊晶薄膜的結構資訊，繞射峰結果顯示，BOSe 薄膜沿 (00L) 方向在單晶基板上生長，且未觀察到任何雜相，如圖 2(b) 所示，並且透過 RSM 的量測 (圖 2(c))，可清楚的觀察 BOSe 薄膜是磊晶生長在 STO 單晶基板上，我們進一步透過 TEM 清楚看到原子級的影像 (圖 2(d))，說明薄膜品質不錯，另外，表面平整度對整合元件特性與製造上會有相當的影響，RHEED 是一種用來實時監控材料成長的技術圖 2(e)，成長前，先定義出 STO 基板晶軸方向 [100] (圖 2(f))，並實時監控成長時繞射條紋的變化，成長後的 BOSe 具有條狀繞射條紋 (圖 2(g-h))，證實所生長之 BOSe 薄膜亦具原子級平整度，有利於後續元件的製作與整合。

圖 2. BOSe 薄膜結構鑑定 (a) 脈衝雷射製程示意圖、(b) XRD 繞射、(c) RSM、(d) TEM 、(e) RHEED 示意圖和 (f-h) RHEED 繞射結果<sup>(15)</sup>。

## 2.2 原生高介電氧化層 (Native high $\kappa$ dielectric oxide layer)

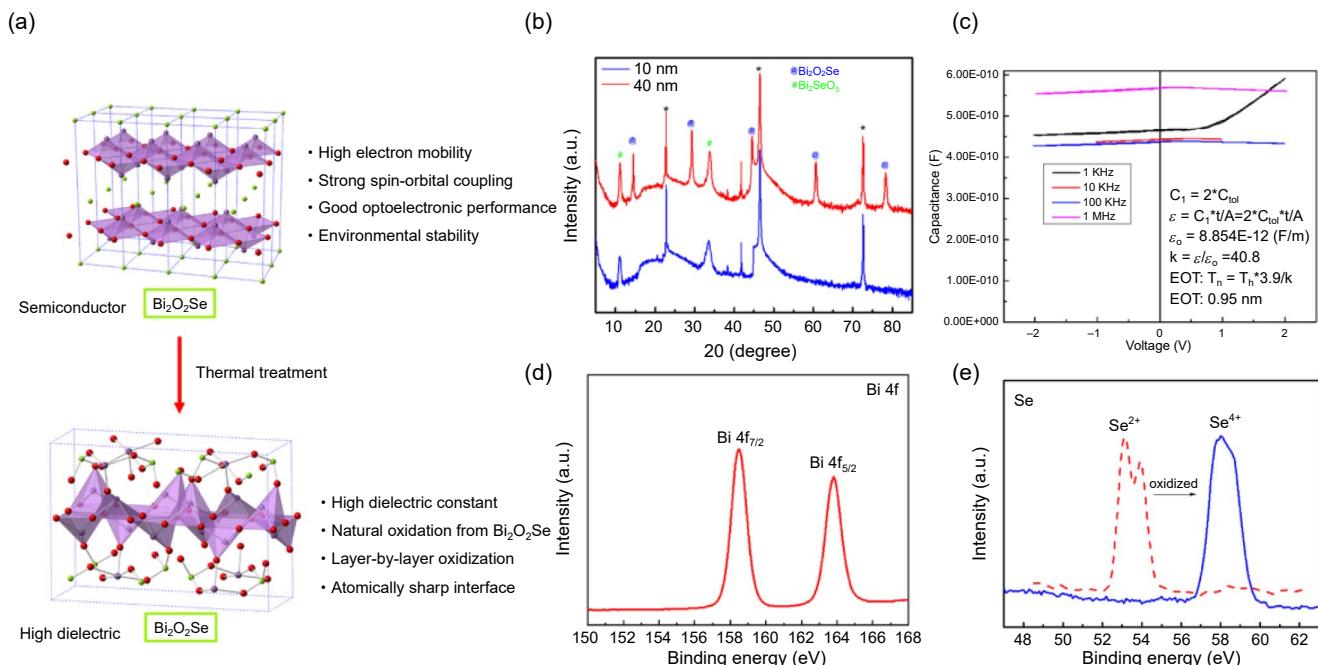

為了在二維 BOSe 材料上形成高品質的原生介電層，目前已開發出三種主要氧化技術：(1) 透過熱退火處理，可將 BOSe 氧化為結晶態 BSO，形成具有原子級銳利介面與可控厚度的氧化層，類似傳統 Si/SiO<sub>2</sub> 系統，且缺陷密度較低，有助於提升元件的穩定性與性能；(2) 其次，氧氣電漿氧化可快速將 BOSe 表面轉化為非晶態 Bi<sub>2</sub>SeO<sub>5</sub>，此方法加工速度快且製作出的場效電晶體具有優異的開關電流比；(3) 紫外線輔助插層氧化，則以 185 nm 紫外光激發臭氧產生活性自由基，在較低溫 (120 °C)、短時間 (3.5 分鐘) 條件下，促進 Se 層插層氧化，同時保留 BOSe 層狀骨架結構，生成層狀且單晶的 BSO 磊晶層，並合成與 BOSe 鱗狀結構晶格匹配的原子級平坦介面，此法不僅適合溫度敏感的元件應用，亦有助於精確整合高介電常數氧化層至通道中，並進一步提升二維電晶體的可靠性與性能。

本研究採用熱退火技術將 BOSe 磷晶薄膜成功氧化，形成原生的 BSO 高介電常數 (high-k) 介電層 (如圖 3(a) 所示)，為驗證氧化效果與結構品質，我們進行了 X 光繞射分析，如圖 3(b) 所示，針對在 STO 基板上形成的 BOSe/BSO 異質結構進行  $\theta$ - $2\theta$  掃描，結果清晰地顯示了來自 BOSe、BSO 的 (00L) 系列繞射峰以及 STO 基板的 (00L) 訊號，且並無其他雜相存在，此結果證實 BOSe 薄膜可透過適當的熱退火製程，將 BOSe 磷晶層氧化成高品質、具特定結晶取向的 BSO 介電層，同時與 STO 基板維持良好的磷晶關係，在此原生 BSO 介電層上，亦可再次磷晶成長 BOSe 半導體層，這對於設計的多層二維材料元件結構是重要的。在介電特性方面，此 BSO 層其等效氧化物厚度可低至 0.95 nm 圖 3(b)，展現出優異的介電性能，具有作為閘極介電層的應用潛力。為進一步確認化學價態的轉變，我們採用了 X 光光電子能譜 (X-ray photoelectron spectroscopy, XPS) 分析 (圖 3(d) 和圖 3(e))，分析結果明確指出，硒 (Se) 元素的價態在氧化前後，從 BOSe 中的 -2 價 (對應圖中紅色光譜線所示) 轉變為 BSO 中的 +4 價 (對應圖中藍色光譜線所示)，此價態的轉變說明 BOSe 已完全氧化成 BSO 介電層，並且確認氧化層中無明顯殘留的半導體相，這些結果說明了熱退火法是製備高品質 BOSe/BSO 異質結構的有效方式。

圖 3. 原生氧化層結構、成分與特性分析：(a) 氧化示意圖、(b) XRD 繞射結果、(c) 介電特性、(d) Bi 能譜和 (e) Se 能譜變化<sup>(15)</sup>。

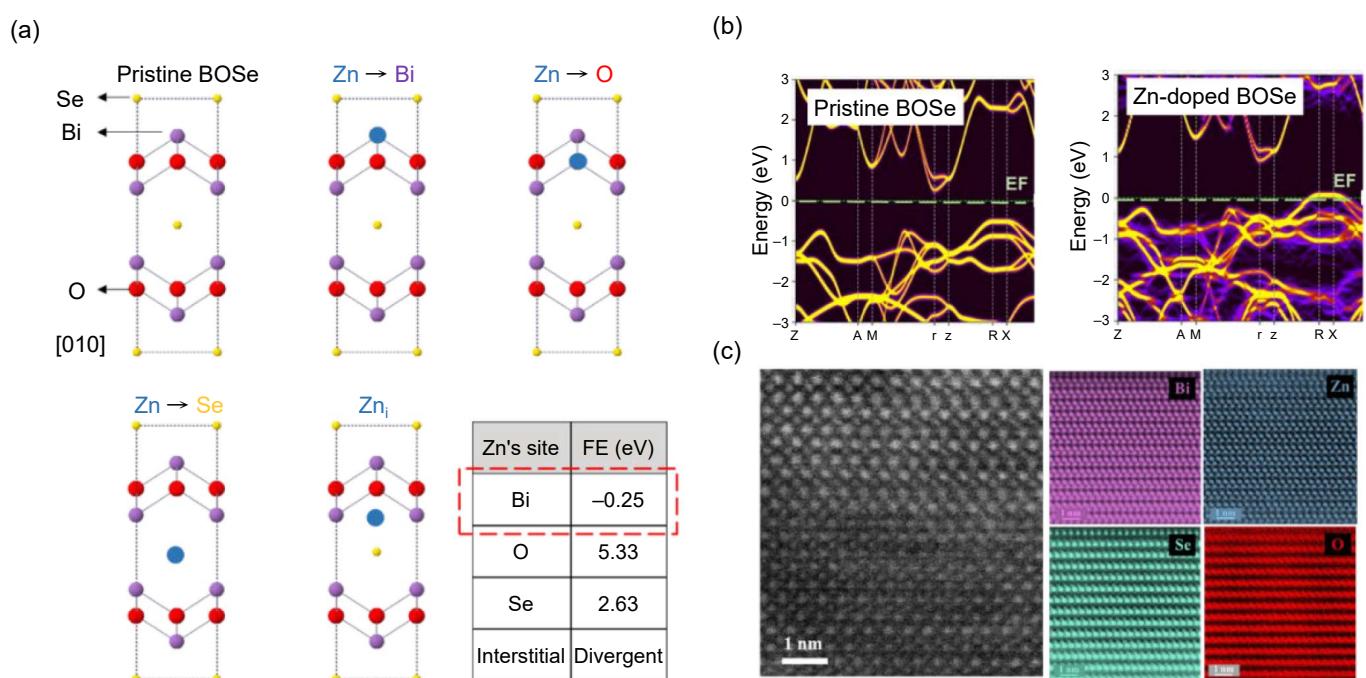

### 2.3 P 型半導體調控

對於潛在的半導體材料，能夠有效調控其載子濃度與導電類型 (N 型或 P 型) 是應用於半導體元件的重要材料特性，針對 BOSe 材料，本研究透過摻雜實現 P 型導電特性，利用缺陷化學原理，將二價的鋅離子 ( $\text{Zn}^{2+}$ ) 引入晶格中取代三價的鉍離子 ( $\text{Bi}^{3+}$ )，預期將會產生電洞作為多數載子，進而獲得 P 型半導體。為此，我們採用了脈衝雷射摻雜 (pulsed laser doping) 技術將 Zn 摻入 BOSe 薄膜中，為了評估 Zn 摻雜的可行性與穩定性，我們進行了第一原理

理論計算，計算模擬了 Zn 原子在 BOSe 晶格中不同位置的可能性，包括取代 Bi、O、Se 原子，以及佔據晶格間隙位置，生成能 (formation energy) 的計算模擬結果顯示於圖 4(a)，Zn 取代 Bi、O 與 Se 時的形成能分別為  $-0.25$  eV、 $5.33$  eV 與  $2.63$  eV，顯示 Zn 取代 Bi 原子構型最為穩定，對應了最低的生成能。此外，Zn 佔據晶格間隙位置的構型在計算中難以收斂，在熱力學上極不穩定，綜合計算結果，Zn 取代 Bi 是能量最低且最穩定的摻雜方式。基於此，我們進一步繪製了純 BOSe 與 Zn 摻雜 BOSe 薄膜 (Zn 取代 Bi 位置) 的能帶結構 (圖 4(b))，透過能量色散光譜 (energy-dispersive spectroscopy, EDS) 對摻雜後的樣品進行了成分分析與空間分佈檢測，如圖 4(c) 所示的 EDS mapping，清楚地解析了各元素的分佈，圖中 Zn 與 Bi 的訊號分佈呈現高度重疊，這驗證了 Zn 原子是以取代 (substitutional) 的方式佔據了原本 Bi 原子的位置，與理論計算預測最穩定的構型一致。

圖 4. (a) Zn 參雜位置能量計算、(b) 能帶比較圖和 (c) TEM 成分分析<sup>(16)</sup>。

## 2.4 互補式金屬氧化物半導體 (complementary metal-oxide-semiconductor, CMOS) 邏輯元件的製備

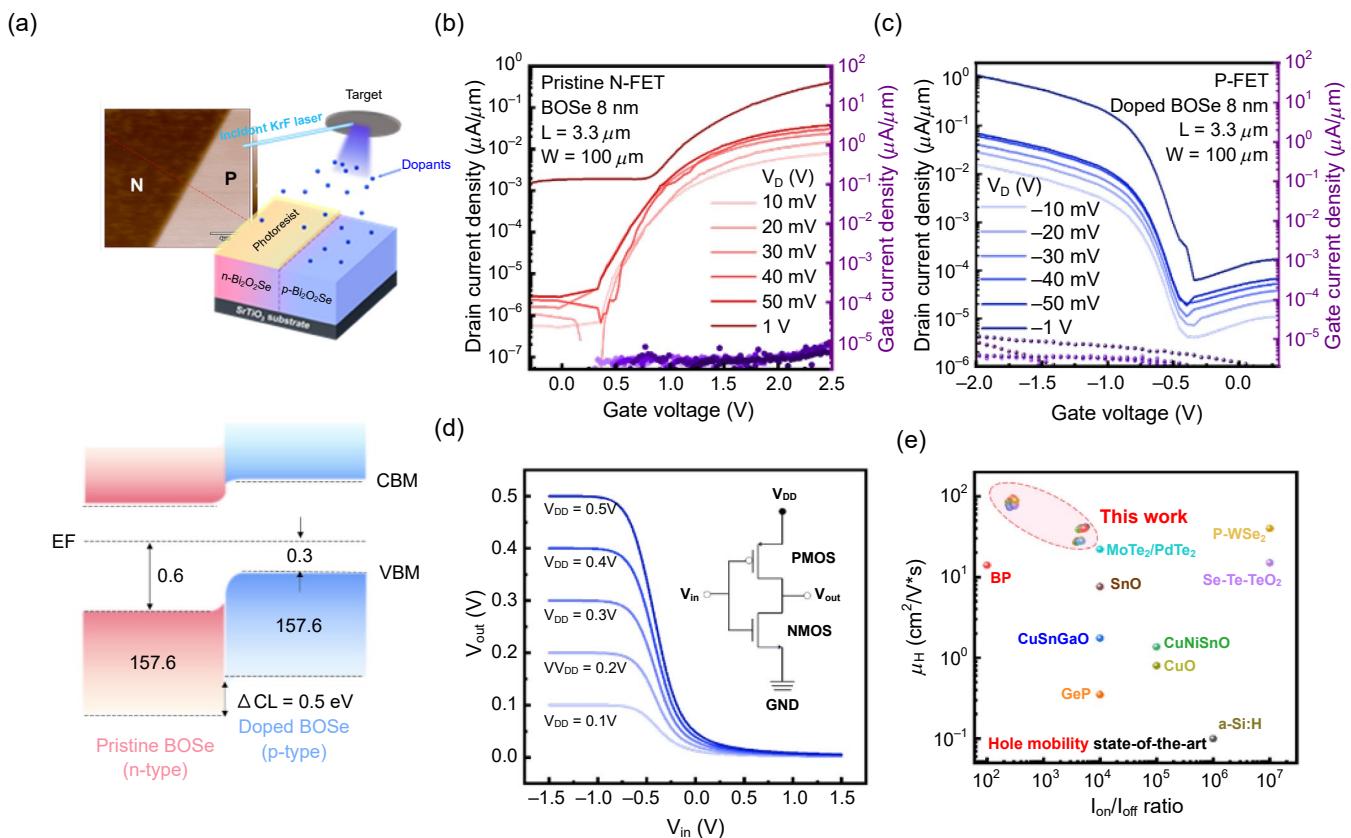

經摻雜的平面式 BOSe/BOSe PN 同質接面，可利用基礎的 BOSe/STO 樣品，結合 DLP 無光罩曝光系統與脈衝雷射摻雜製程，在 BOSe 層上定義出 P 型區域，在此同質接面施加偏壓，可以得到典型的 PN junction 整流的特性，利用表面電位顯微鏡 (Kelvin probe force microscopy, KPFM) 量測，可觀察到 P 型區與 N 型區有清晰的對比差異，說明 PN 區域表面電位差約為  $0.35$  eV，對於能隙約  $0.8$  eV 的 BOSe 而言， $0.35$  eV 的電位差足以改變費米能階 (Fermi level)，在能隙中的相對位置 (圖 5(a))，從而導致載子極性的轉變 (由 N 型變為 P 型)，同時這也說明，透過選擇合適的摻雜元素，可以調整材料的導電特性。為探索此材料系統帶來了更多可能性，利用前述所提出雷射摻雜技術搭配微影製程，有助於製作 BOSe/BSO/Nb:STO 異質結構的場效電晶體，N 型電晶體的轉移曲線呈現出典型的 n 型行為 (圖

5(b))，其開關電流比約為  $4 \times 10^5$ ，且汲極電流在閾值以下具有陡升的變化，其次臨界斜率約為  $68 \text{ mV/dec}$ ，接近  $300 \text{ K}$  熱力學極限  $60 \text{ mV/dec}$ ，另一方面，P 型電晶體的轉移曲線(圖 5(c))在不同 VDS 條件下均觀察到汲極電流的明顯上升，其開關比約為  $5 \times 10^3$ ，場效電洞遷移率達  $34 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}$ ，根據結果，合成之 P 型電晶體的最大場效遷移率約為  $83 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}$ ，且閾值電壓保持在約  $-0.8 \text{ V}$ ，藉由極性調控的優勢，展示 CMOS 反相器電路(圖 5(d))其操作電壓介於  $0 \text{ V}$ (邏輯狀態 0)與  $1 \text{ V}$ (邏輯狀態 1)之間，圖 5(e)將本元件的開關電流比以及電洞遷移率，與其他 P-FET 進行比較，以 BOSe 為基礎的 P 型電晶體不僅具有更高的電洞遷移率，且仍能維持適中的開關比，透過這些設計與製程，元件特性可以調控以滿足更多元的應用需求。

圖 5. (a) 雷射參雜與 CMOS inverter 示意圖、(b) N-FET 轉移曲線、(c) P-FET 轉移曲線、(d) CMOS inverter 電壓轉移曲線和 (e) 場效電洞遷移率比較<sup>(16)</sup>。

## 2.5 硼基元件整合

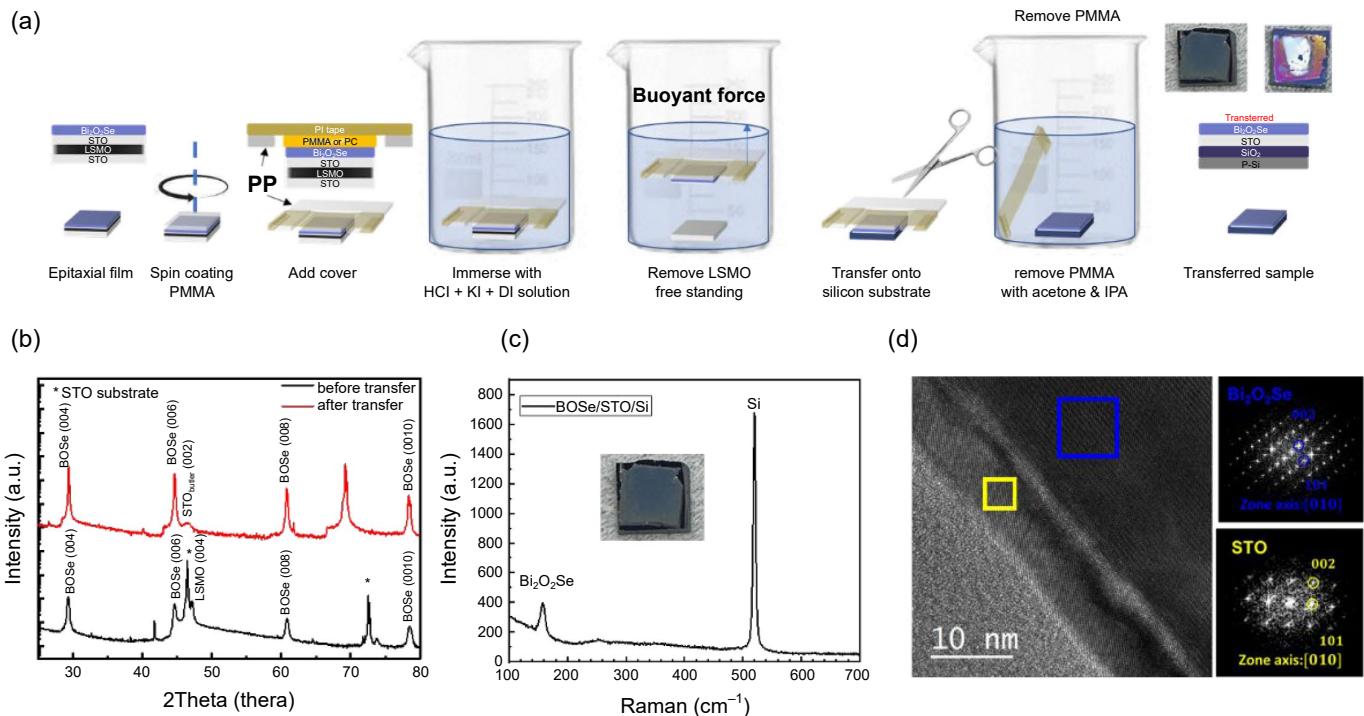

矽基板由於與標準黃光製程的高度相容性，在二維材料領域中被廣泛應用，前述的成果中，成功地將 BOSe 及其原生高介電常數氧化層整合成先進電子元件，展現了鉻氧化合物的獨特物理特性，為進一步拓展其應用的可能，團隊進一步採用自支撐技術(圖 6(a))將 BOSe 薄膜轉移至矽基板，成長時在 BOSe 薄膜與單晶基板之間，插入一層可被溶解的犧牲層，在 BOSe 薄膜表面旋塗高分子聚合物聚甲基丙烯酸甲酯 (polymethyl methacrylate, PMMA) 作為機械支撐層，隨後將樣品浸泡在蝕刻液 ( $\text{HCl} + \text{KCl}$ ) 中，待犧牲層溶解完畢後，可將附

著 PMMA 上的 BOSe 薄膜轉移至目標矽基板，最後以丙酮跟 IPA 移除 PMMA 支撐層，即可成功將 BOSe 磺晶薄膜轉移至矽基板上，透過 X 光繞射 (圖 6(b))、拉曼光譜 (圖 6(c)) 以及穿式電子顯微鏡 (transmission electron microscopy, TEM) (圖 6(d)) 等結構分析量測，證實了轉移後薄膜仍維持了良好的結晶品質，說明此轉移技術具備於矽基元件上應用的可行性，為後續在矽平台上進行 BOSe 相關研究發展的可能性。

圖 6. 自支撐 BOSe 薄膜/Si 基板 (a)自支撐 BOSe 薄膜轉移流程、(b) XRD 繞射、(c) 拉曼光譜量測和 (d) TEM 繞射圖<sup>(15)</sup>。

## 2.6 異質結構整合

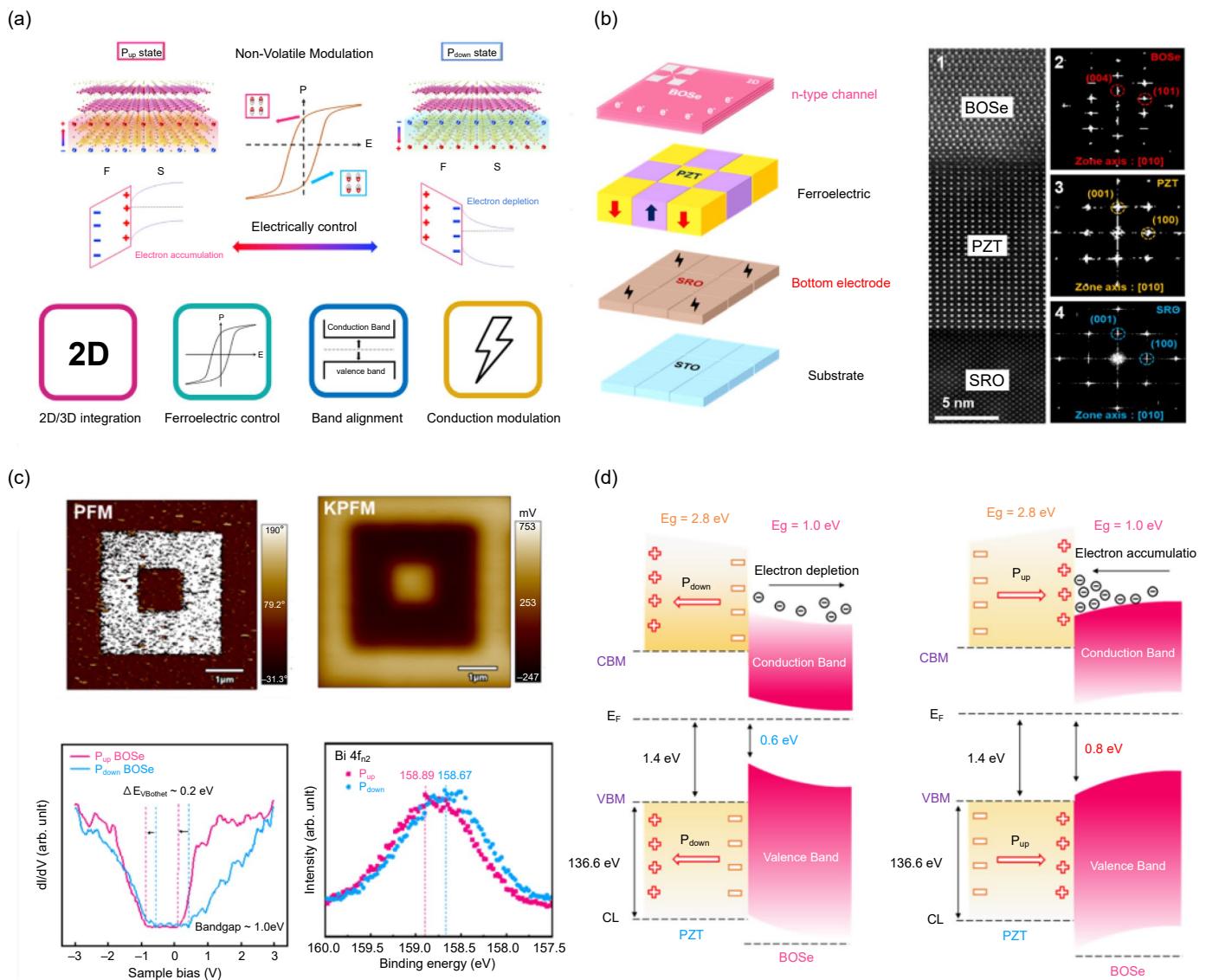

隨著 AI 與邊緣運算需求增加，鐵電電晶體 (ferroelectric field-effect transistor, FeFET) 成為關鍵元件，利用鐵電材料極化特性，即使在無通電的情況下仍能保有資料狀態，解決傳統記憶體揮發性限制，並能有效改變半導體的物理特性，以實現低功耗與高速運算 (圖 7(a))。近期研究指出 BOSe 在特定條件下可能具有鐵電性，但鐵電材料對 BOSe 的調控尚無深入探討，利用誘導鐵電性與表面電荷靜電效應，調控 BOSe 的導電性與能帶結構，可實現非揮發且可逆的控制，提升 BOSe 系統於記憶體與運算元件的應用潛力。由於 BOSe 與鈣鈦礦材料具有良好晶格匹配，我們在 BOSe 之下加入一層鐵電  $\text{PbZr}_{0.2}\text{Ti}_{0.8}\text{O}_3$ (PZT) 層形成 BOSe/PZT/SrRuO<sub>3</sub>(SRO)/SrTiO<sub>3</sub><sup>(16)</sup> 異質磊晶結構，利用 PZT 提供的極化場來調控能帶結構，進而實現非揮發性與可逆性的能力，選擇 PZT ( $a = b = 3.954 \text{ \AA}$ ,  $c = 4.089 \text{ \AA}$ , 正方晶系) 作為鐵電層，不僅是 PZT 具有優異的極化能力，且其  $a$  軸的晶格常數與 BOSe ( $a = b = 3.891 \text{ \AA}$ ,  $c = 12.213 \text{ \AA}$ , 正方晶系) 高度匹配，高解析 STEM 與 FFT 繞射圖 (圖 7(b)) 顯示各層具銳利介面及良好磊晶關係。

BOSe 層中的費米能階位置可利用鐵電極化被有效調控，不同極化狀態  $P_{up}$  和  $P_{down}$  將於介面處產生內建電場，使能帶彎曲與改變載子濃度，有助於 FeFET 元件的開發，結合 BOSe 的高場效遷移率以促進高速資料運算。透過導電 AFM 於 PZT 表面施加 +8V / -8V 寫入 box-in-box 極化圖案 (圖 7(c))，利用 PFM 觀察局部極化方向翻轉，KPFM 測得  $P_{up}$  與  $P_{down}$  區域表面電位差  $\sim 0.2$  eV，說明 PZT 不同極化狀態對 BOSe 表面電子位能的調控。進一步以同步輻射中心的高解析 XPS 進行 Bi 4f 能階量測 (圖 7(d))，發現  $P_{up}$  與  $P_{down}$  區域束縛能分別為 158.89 eV 與 158.67 eV，相差約 0.22 eV，與 KPFM 結果吻合。對於 N 型 BOSe， $P_{down}$  使能帶向上彎曲，形成電子空乏層降低導電性； $P_{up}$  使能帶向下彎曲，形成電子累積提升導電性，驗證了利用 PZT 鐵電層的非揮發性極化狀態，可有效且可逆地調控上方 BOSe 半導體層的電子位能、能帶結構及載子濃度，此結果不僅展示了以鐵電閘極調控二維半導體的可行性，也為開發新型非揮發性記憶體元件開啟了新的研究方向與應用可能。

圖 7. (a) 鐵電調控極化示意圖、(b) TEM 繞射分析、(c) 表面電位與能階分析和 (d) 不同極化方向能帶示意圖<sup>(17)</sup>。

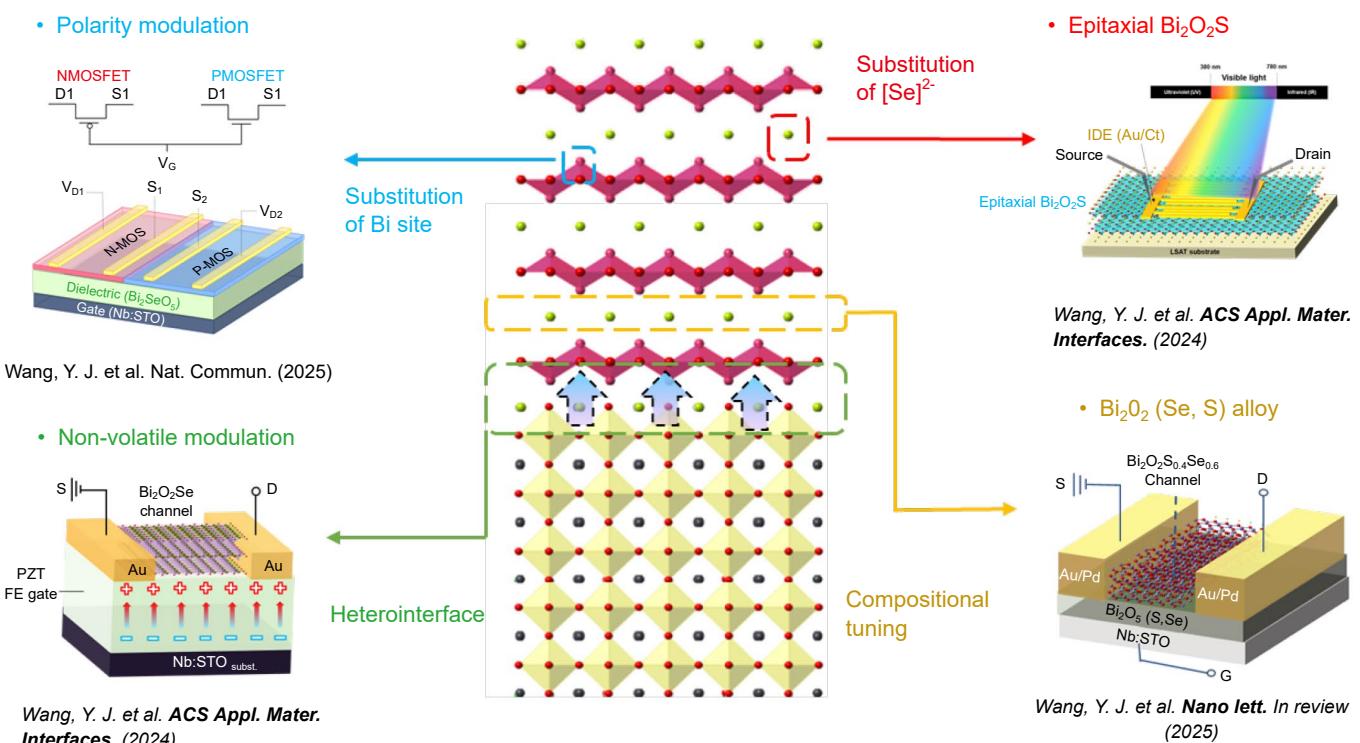

### 三、總結

綜合本研究結果，BOSe 展現出優異的物理特性，且其原生氧化層可自然形成高介電常數的介電層，進而有效整合於高效能電晶體結構中，透過脈衝雷射沉積技術的優勢，可迅速調控準二維材料的組成與結構，例如本研究中所展示的極化控制與異質結構設計，此外，藉由針對硫族元素的取代與成分調控，能進一步調整材料性質，拓展 BOSe 及其相關化合物半導體材料的應用潛力，本研究提供了一個有效的平台，促進此類準二維層狀氧化物半導體材料的成長與應用開發。

圖 8. 準二維半導體特性調控與製備<sup>(16-18)</sup>。

### 參考文獻

1. Tan, C. et al., *Nature*, **616**, 66 (2023).

2. Yu, M. et al., *Nature Communications*, **15**, 3622 (2024).

3. Tang, J. et al., *Nature Materials*, **24**, 519 (2025).

4. Wang, W. et al., *Advanced Materials* **35**, 2210854 (2023).

5. Wu, M. & Zeng, X. C. *Nano letters*, **17**, 6309 (2017).

6. Ruleova, P. et al., *Materials Chemistry and Physics*, **119**, 299 (2010).

7. Li, T. & Peng, H., *Accounts of Materials Research*, **2**, 842 (2021).

8. Wu, J. et al., *Nature Nanotechnology*, **12**, 530 (2017).

9. Li, T. et al., *Nature Electronics*, **3**, 473 (2020).

10. Tan, C. et al., *Nano Letters*, **22**, 3770 (2022).

11. Kang, M. et al., *ACS nano*, **15**, 8715 (2021).

12. Liang, Y. et al., *Advanced Materials*, **31**, 1901964 (2019).

13. Pan, L. et al., *ACS applied materials & interfaces*, **11**, 21603 (2019).

14. Song, Y. *et al.*, *Nanotechnology*, **31**, 165704 (2020).

15. Lu, H.-B., *National Yang Ming Chiao Tung University*, (2024).

16. Wang, Y.-J. *et al.*, *Nature Communications*, **16**, 1 (2025).

17. Wang, Y.-J. *et al.*, *ACS Applied Materials & Interfaces*, **16**, 27523 (2024).

18. Wang, Y.-J. *et al.*, *ACS Applied Materials & Interfaces*, **17** (14), (2025).

## 作者簡介

陳怡誠先生為國立陽明交通大學材料與科學工程學系博士，現為國立臺灣師範大學物理學系助理教授。

Yi-Cheng Chen received his Ph.D. in Materials Science and Engineering from National Yang Ming Chiao Tung University. He is currently an Assistant Professor in the Department of Physics at National Taiwan Normal University.

王詠鈞先生為國立清華大學材料科學工程學系博士。

Yong-Jyun Wang received his Ph.D. in the Department of Materials Science and Engineering from National Tsing Hua University.

朱英豪先生為國立清華大學材料科學工程學系博士，現為國立清華大學材料科學工程學系講座教授。

Ying-Hao Chu received his Ph.D. in the Department of Materials Science and Engineering from National Tsing Hua University. He is a Chair Professor in the Department of Materials Science and Engineering at National Tsing Hua University.